一、PCB布局布線的建議的意義

PCB布局布線的建議是一個高附加值的任務(wù),它的目的在于完成高EMC性能PCB 設(shè)計,同時將由于EMC問題而產(chǎn)生的PCB布局布線成本最小化。PCB布局布線的建議 的核心包括以下三方面:

l 指出關(guān)鍵EMC器件的在PCB中的相對位置;

l 指岀PCB中哪些區(qū)域需要進行完整的地平面設(shè)計,并將該地平面的阻抗最小化;

l 串擾防止的處理。

它的具體內(nèi)容包括兩方面:

l 書面的建議描述;

l PCB布局布線建議示意圖。

完成PCB布局布線建議后,在電子工程師將原理圖送到CAD小組進行布局布線設(shè)計 前,EMC專家需要與CAD的專家和工程師進行充分的溝通,將所需表達的意見充分傳 達給CAD的專家和工程師。

二、PCB層數(shù)及各層的分配

從EMC方面考慮,除非2層板也能設(shè)計出較為完整地平面,否則最好采用帶有地層 和電源層的4層以上的PCB。實踐證明,4層板與2層板相比,4層板能取得高于2層板 100%的EMC性能。但要注意:4層板以上,并非層數(shù)越多越好。2層板通常地平面很難 設(shè)計完整,如果使用2層板,那么工程師要特別注意地平面的設(shè)計。

PCB層排布的一般原則:

l?元件面下面(第2層)為地平面,提供器件屏蔽層以及為頂層布線提供參考平面;

l 所有信號層盡可能與地平面相鄰;

l 盡量避免兩信號層直接相鄰;

l 主電源盡可能與其對應(yīng)地相鄰。

4層PCB層的層排布方式見表

| 方案 | 電源層數(shù) | 地層數(shù) | 信號層數(shù) | 1 | 2 | 3 | 4 |

| 1 | 1 | 1 | 2 | S | G | P | S |

| 2 | 1 | 1 | 2 | G | S | S | P |

| 3 | 1 | 1 | 2 | S | P | G | S |

方案1為4層PCB的主選層設(shè)置方案,在元件面下有一地平面,關(guān)鍵信號優(yōu)選布TOP層。至于層厚設(shè)置,有以下建議:

?滿足阻抗控制。

?芯板(GND到POWER)不宜過厚,以降低電源、地平面的分布阻抗;保證電源平面的去耦效果。為了達到一定的屏蔽效果,有人試圖把電源、地平面放在TOP、BOTTOM層,即采

用方案2。用此方案往往是試圖達到想要的屏蔽效果,但至少存在以下缺陷:

?電源、地相距過遠,電源平面阻抗較大。

?由于元件焊盤等影響,電源、地平面極不完整。

?由于參考面不完整,信號特性阻抗不連續(xù)。

實際上,對于PCB中器件越來越密的情況下,本方案的電源、地幾乎無法作為完整的參考平面,預(yù)期的屏蔽效果很難實現(xiàn)。方案2的使用范圍有限。但在個別單板中,方案2不失為最佳層設(shè)置方案。

方案3同方案1類似,適用于主要器件在BOTTOM布局或關(guān)鍵信號底層布線的情況;一般情況下,限制使用此方案。

6層PCB層的層排布方式見表

| 方案 | 電源 | 地 | 信號 | 1 | 2 | 3* | 4 | 5 | 6 |

| 1 | 1 1 | — 1 |

4 | S1 | G | S2 | S3?> | P | S4 |

| 2 | 1 | 1 | 4 | S1 | S2 | G | P | S3 | S4 |

| 3 | 1 | 2 | 3 | S1 | G1 | S2 | P | G2 | S3 |

| 4 | 1 | 2 | 3 | S1 | G1 | S2 | G2 | P | S3 |

對于6層板,優(yōu)先考慮方案3,優(yōu)選布線層S2,其次S3、S1。主電源及其對應(yīng)的地布在4、5層,層厚設(shè)置時,增大S2?P之間的間距,縮小P?G2之間的間距(相應(yīng)縮小G1?S2層之間的間距),以減小電源平面的阻抗,減少電源對S2的影響。

在成本要求較高的時候,可采用方案1,優(yōu)選布線層SI、S2,其次S3、S4,與方案1 相比,方案2保證了電源、地平面相鄰,減少電源阻抗,但SI、S2、S3、S4全部裸露在 外,只有S2才有較好的參考平面。對于局部、少量信號要求較高的場合,方案4比方案3更適合,它能提供極佳的布線 層S2。

8層PCB層的層排布方式

| 方案 | 電源 | 地 | 信號 | 1 | 2 | 3 | 4?. | 5?j | 6 | 7 | 8 |

| 1 | 1 | 2 | 5 | S1 | G1?? | S2 | 'S3 ; | P | S4 | G2 | S5 |

| 2 | 1 | ,3 | 4 | S1 | -?G1 | S2 | G2?- | P?” | S3 . | G3?1 | 'S4 -1 |

| 3 | 2 | 2、 | :4.. | S1 . | ;G1 | S2 | P1 | G2 | S3 . | P2 R | S4 |

| 4 | 2 | 2 | 4 | S1?: | G1 | S2 | P1 | P2 | S3?, | G3 | S4 |

| 5 | 2 | 2 | 4 | S1 | G1 | P1 | S2 | S3 | G2 | P2 | S4 |

對于單電源的情況下,方案2比方案1減少了相鄰布線層,增加了主電源與對應(yīng)地相鄰,保證了所有信號層與地平面相鄰,代價是犧牲一布線層;對于雙電源的情況,推薦采 用方案3,方案3兼顧了無相鄰布線層、層壓結(jié)構(gòu)對稱、主電源與地相鄰等優(yōu)點,但S4 應(yīng)減少關(guān)鍵布線;方案4無相鄰布線層、層壓結(jié)構(gòu)對稱,但電源平面阻抗較高,應(yīng)適當加 大3?4、5?6之間層間距,縮小2?3、6?7之間層間距;方案5與方案4相比,保證了 電源、地平面相鄰,但S2、S3相鄰,S4以P2作參考平面,對于底層關(guān)鍵布線較少以及S2、S3之間的線間串擾能控制的情況下此方案可以考慮。

三、地平面和電源平面在PCB層中的位置

層的放置以電快速瞬變脈沖群測試原理為基礎(chǔ),通過對共模電流流向的分析來確定。

對于浮地設(shè)備來說,大多數(shù)情況下,可以把GND層當成是屏蔽層,用來泄放共模干擾電 流,AGND必須放置在沒有被共模干擾耦合到的層和位置。(注:這里描述的AGND通 常為產(chǎn)品中的模擬電路,其電平較低,噪聲容限較低,較容易受干擾。)

PCB電源的層數(shù)由其電源種類數(shù)量決定。對于單一電源供電的PCB, 一個電源平面足夠 了;對于多種電源,若互不交錯,可考慮采取電源層分割(保證相鄰層的關(guān)鍵信號布線不跨 分割區(qū));對于電源互相交錯(尤其是像8260等IC,多種電源供電,且互相交錯)的單板, 則必須考慮采用2個或2個以上的電源平面,

每個電源平面的設(shè)置需滿足以下條件:

l 單一電源或多種互不交錯的電源;

l 相鄰層的關(guān)鍵信號不跨分割區(qū)。

地的層數(shù)除滿足電源平面的要求外,還要考慮:

l 元件面下面(第2層或倒數(shù)第2層)有相對完整的地平面;

l 高頻、高速、時鐘等關(guān)鍵信號有一相鄰地平面。

l 關(guān)鍵電源有一對應(yīng)地平面相鄰。

四、指出敏感元器件在PCB中放置的相對位置

敏感元器件一般放置在電路板的當中位置,并且在PCB中沒有耦合的層上,例如圖&10?中,信號及元件面1為沒有耦合的面,這一層中沒有共模電流流過。信號及元件面2為存在共 模電流耦合的層,這一層中共模電流會流過,自然器件置于該層中,將受更嚴重的干擾。

五、濾波電容等濾波器件在PCB中的相對放置

濾波電容通常放置在被濾波器件的相應(yīng)管腿附近,或在共模電流泄放的路徑中。所有?的濾波電容的連接不能用長線的方式,而要保證低阻抗的連接,比較好的做法是,濾波電容引線長寬比小于3,至少要做到小于5。

六、地平面的設(shè)計

共模電流流過的區(qū)域必須具有完整的地平面,完整地平面意味著一塊沒有任何過孔、?開槽、裂縫且長寬比小于3的PCB銅箔。以下幾個地方通常需要使用完整地平面:

(1)共模電流的泄放路徑上;

(2)有共模電流流過的兩個器件的地管腿之間;?⑶ 端口上的濾波器電容、芯片去耦電容、旁路電容與地之間的互連線。

為了更好地實現(xiàn)PCB中的完整地平面設(shè)計,建議在PCB布局確定后,先將所需要的

完整地平面布置好,并將需要進行完整地平面設(shè)計的區(qū)域設(shè)定為不能有任何過孔、開槽、?裂縫等的區(qū)域,然后進行印制線布線設(shè)計。這樣可以防止先把印制線布置好后,發(fā)現(xiàn)某區(qū)?域的地平面不完整,而再進行修改帶來的時間浪費(通常這個時候再進行修改,難度也會?增加)。(注:當共模電流流過GND時,并不是整個PCB的GND平面需要完整地平面,這也

是不可行的,只是在以上3點描述的地方需要完整地平面。)

七、模擬地地平面的設(shè)計

這里所述的模擬地AGND通常是產(chǎn)品中電平較低、對干擾比較敏感的電路的參考地。該平面必須設(shè)計在既沒有共模耦合、也沒有共模電流流過的位置上。如果沒有辦法避免共 模電流流過AGND,那么共模電流流過的路徑必須為完整地平面(完整地平面意味著一 塊沒有任何過孔、開槽、裂縫且長寬比小于3的PCB銅箔)。

八、電源平面的設(shè)計

電源是產(chǎn)品電路的主電源,該平面通常在保證沒有串擾發(fā)生的情況下盡可能大。?并且VCC平面盡量做到與GND地平面鄰近,以增加電源平面與地平面之間的層間電容, 這對高頻去耦有效。

九、串擾防止的處理方式

“臟”(紅色)的信號線、特殊處理的時鐘信號線、高速信號線(特殊顏 色)與“干凈”(綠色)信號線之間必須考慮串擾問題,處理串擾的方式一般有:

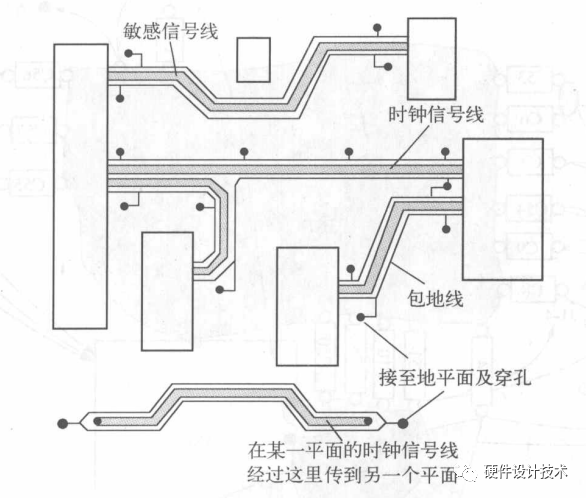

l 對信號線進行包地(圖8-11)處理,在互為串擾的信號線之間插入地線。

l 把信號線分布在不同的層中,其間有GND地層隔離。同一層中左右布置且沒有 包地、相鄰層的上下平行布置,都認為存在串擾。

l 信號線下方必須有地平面。

十、特殊信號線(如時鐘信號線、高速信號線、敏感信號線等)的處理方式

給出表列出的時鐘信號線、敏感信號線、高速信號線等的布線注意方法,包括阻抗匹配、串擾等。始端阻抗匹配的電阻和限流電阻通常放置在信號發(fā)出端。在?串擾處理上,除了考慮這些信號線在PCB中的具體位置之外,通常還應(yīng)釆用屏蔽地線包地的方式處理。

十一、PCB中空置區(qū)域的處理

所有空置區(qū)域都要鋪銅處理,并將其通過適量過孔與相應(yīng)區(qū)域的地平面相連。

十二、其他建議

列出其他建議。

PCB布局布線示意圖

畫出PCB布局布線示意圖是為了更直觀地表達以上PCB布局布線的建議,并把一些 用文字很難清楚表達的建議用示意圖的方式表示出來。它所包含的內(nèi)容是為了讓CAD專 家和工程師更容易理解。一般在該PCB布局布線示意圖中,將表達出完整地平面(沒有 過孔、開槽、裂縫,長寬比小于3)在PCB中及與器件的相對位置,I/O端口上的濾波電 容、器件的去耦電容與器件、完整地平面的相對位置,及“臟”信號線、“干凈”信號線。

PCB設(shè)計審查與EMC風險評估

一、PCB設(shè)計審查的意義和任務(wù)

PCB審查的目的是為了檢查PCB設(shè)計者是否將EMC專家給出的PCB布局布線建議 落實。縱然將全部PCB布局布線的建議都落實會有很大的困難,但是通過審查,EMC專 家與CAD的專家一起能找到一種比較折中的方法,這種折中的方法,不但能使EMC風 險降低,而且還能順利實現(xiàn)PCB布局布線。在PCB審查結(jié)果中,EMC專家需要把一些 未落實的或?qū)嶋H實現(xiàn)與建議不一致的現(xiàn)象一一列出,這將有助于產(chǎn)品在EMC測試時定位 分析。列出的內(nèi)容主要包括如下3個方面:

l?共模電流流過路徑上的阻抗,如地平面是否完整,是否沒有任何過孔、裂縫

l 和開槽。.'

l “臟”信號印制線及一些需要進行特殊處理的信號印制線與其他信號線之間是否 存在串擾。

l 去耦、旁路電容和濾波電容位置是否合理,引線阻抗是否足夠低。

二、地平面完整性及其阻抗審查

(1)如果地平面的設(shè)計沒有按照PCB布局布線的建議執(zhí)行,那么按表所示的格式 指出不同點,并說明風險在哪里。

| 序?號 | 原建議描述 | 實際處理方式 | 風險點描述 |

| 1 | |||

| 2 | |||

| 3 |

(2)對有可能出現(xiàn)風險的點,按表所示的格式列出可行的修改建議。

| 序?號 | 可行的修改建議 |

| 1 | |

| 2 | |

| 3 |

三、串擾審查

(1)如果串擾防止設(shè)計沒有按照PCB布局布線的建議執(zhí)行,那么按表所示的格 式指出不同點,并說明風險在哪里。

| 序?號 | 原建議描述 | 實際處理方式 | 風險點描述 |

| 1 | |||

| 2 | |||

| 3 |

(2)對有可能出現(xiàn)風險的點,按表所示的格式列出可行的修改建議。

| 序?號 | 可行的修改建議 |

| 1 | |

| .?2 | |

| 3 |

四、去耦、旁路電容和濾波電容的審查

是否將PCB布局布線建議中關(guān)于去耦一旁路一濾波電容的建議落實?若有不同的地

方,那么:

(1)如果去耦一旁路電容和濾波電容在PCB中設(shè)計(主要是去耦電容的位置是否靠 近被去耦器件電源管腳,并保證引線阻抗足夠低,如引線長寬比小于3;旁路電容位置是

否在共模電流泄放的最佳位置上,并保證引線阻抗足夠低,如引線長寬比小于3;濾波電 容是否放置在I/O端口上,同時在共模電流泄放的最佳位置上,并保證引線阻抗足夠低, 如引線長寬比小于3)沒有按照PCB布局布線的建議執(zhí)行,那么按表所示的格式指出不同點,并說明風險在哪里。

| 序號 | 電容代號 | 原建議描述 | 實際處理方式 | 風險點描述 |

| 1 | ||||

| 2 | ||||

| 3 | ||||

| 4 |

(3)對有可能出現(xiàn)風險的點,按表所示的格式列出可行的修改建議。

| 序號 | 電容代號 | 可行的修改建議 |

| 1 | ||

| 2 | ||

| 3 |

五、PCB布局布線文件

為了保持完整性,建議把PCB布置圖分層列出,圖X?圖X是按圖Y所示的設(shè)計建議所完成的PCB布置圖的實例。