FPGA已經變得如此成本效益的,它們越來越多地與微控制器配合使用,以提高整個系統的效率。使用包括添加額外的功能在電路板空間最小,增加功率高效處理的復雜算法的前端,聚集多個外部設備卸載高性能MCU或以適應現有的設計到新所需的“膠水”邏輯接口要求,FPGA可提供額外的靈活性往往缺乏標準的MCU。本文將快速瀏覽一些最流行的應用,FPGA和微控制器的“配對”來展示如何提高系統效率,通過降低功耗,減少電路板空間,提高了處理性能,接口靈活性可能能夠顯著地提高你的下一個設計。

FPGA成為MCU配套設備

多久的MCU您選擇為您的設計只是不太有所有的接口通道,你需要?或者,也許你最初的選擇單片機適合剛剛完美,但一個新的需求來了,因為你最好的客戶希望他們的最新設計一些額外的接口。你也許能夠使用更復雜的MCU,而這可能會導致增加顯著的電路板空間(因為它只有在高引腳數封裝),提高了功率(因為它僅適用于更多的閃存和SRAM比你真正需要的),或者更高的成本(對于以前的原因)。

圍繞這個難題的一種方法是通過添加一個FPGA旁邊的MCU規劃需要額外的接口。該FPGA可以方便地提供額外的接口,只是你需要的,同時限制增加了電路板空間,成本和功耗。事實上,相對于使用更復雜的MCU的選擇,您通常最終會用更少的電路板空間,更低的成本和更少的功率。

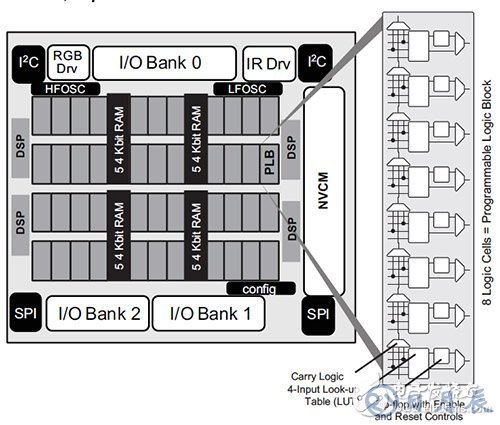

例如,萊迪思的iCE40超低功耗FPGA可提供多達26個信號的IO在一個非常小的2.078毫米由2.078毫米電路板面積,而且因為這些設備通過片上NVM配置,您不需要額外的電路板空間為配置的設備。這些FPGA也有兩個專用I2C接口,并用大量的可配置邏輯的兩個專用SPI接口的添加為更多的接口,為您的應用程序將需要(直到用完針)。萊迪思ICE5LP1K-SWG36ITR50的框圖如圖1所示。

萊迪思FPGA iCE5LP的框圖

圖1:萊迪思FPGA iCE5LP框圖。 (萊迪思半導體公司提供)

該裝置還具有高達80千位的嵌入式RAM塊可用于接口的FIFO緩沖器和因此MCU可以等到整個數據包準備好進行處理。 DSP模塊也可以被用來做低級別的數據處理上的原始傳感器數據作為先于數據發送到MCU一個預處理步驟。當FPGA可以智能地聚合數據中斷的MCU之前,極大地降低了MCU電源是可能的。此外,萊迪思的iCE5LP FPGA已經被設計為非常低功率應用僅為71μA核心電源的靜態電流。添加更多的接口,幾乎不需要額外的電路板空間和功耗。看看你最喜歡的微控制器和高引腳數版本之間的當前價格差,然后把它比作萊迪思FPGA iCE5PL1K價格上向Digi-Key的網站,看看有什么成本節約也可能會提供。

快速響應FPGA接口的請求

當使用FPGA同伴設備能夠快速FPGA的服務請求響應也可以是重要的。例如,音頻接口可能需要具有比傳感器數據更高的優先級訪問,因為在音頻數據的“失速”必須避免或用戶體驗可顯著降低。在一般情況下,能夠支持多種中斷優先級可幫助提高了FPGA的伴侶的實用性,進一步提高系統的整體性能和能效。

有效利用DMA還可以進一步幫助卸載MCU和提高工作效率。例如,也許在FPGA可以首先緩沖向上的前處理的原始數據的完整數據分組,以減少需要被存儲和發送的消息的大小。該FPGA可中斷的MCU,并啟動DMA傳輸是將整個郵件到MCU內存。一旦DMA傳輸完成并且整個消息準備處理中,CPU可以中斷和消息的高層處理可以開始。

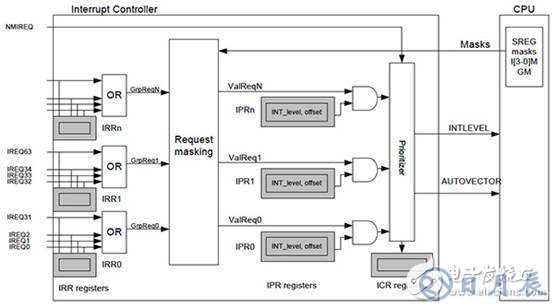

愛特梅爾32位AT32UC3A MCU,例如,具有一個DMA控制器和一個中斷控制器,無論是可編程優先級。中斷控制器圖,對圖2的左側所示,具有在右側一個優先塊,在產生中斷級別到CPU。優先級塊選擇具有最高優先級的中斷,如中斷優先級寄存器(IPRn)與每個相關聯的所定義的中斷級字段中斷源。因此,較高優先級的源,例如一個實時音頻接口,可以被分配的優先級高于低頻傳感器,也許在I2C端口,用于保證更快的處理。

為愛特梅爾MCU AT32UC3A中斷控制器圖片

DMA控制器的形象,為愛特梅爾MCU AT32UC3A

圖2:中斷控制器和DMA控制器框圖為愛特梅爾MCU AT32UC3A。 (愛特梅爾提供)

該AT32UC3A MCU的DMA控制器,框圖,其中顯示在圖2右側的,連接到許多不同的外圍設備,在右側的DMA框圖所示。外圍DMA控制器優先基于與每個外設相關的DMA通道數的每個外設DMA請求(外設被分配到一個信道由一個配置寄存器,因此它們是完全可編程的)與具有較高優先級較低的信道號。這允許DMA傳輸可以很容易地進行分組,并為最有效的數據傳送可能優化。優先級,甚至可以當重新分配算法青睞一種類型的轉移在另一個的部分。

傳感器融合進一步提高系統效率

如前所述,FPGA的可用于通過采用DSP技術來預先處理傳感器數據。特別是,FPGA,具有DSP塊可以實現許多共同的過濾算法中,例如有限脈沖響應(FIR)濾波器,無限脈沖響應(IIR)濾波器和快速傅立葉變換(FFT)。由于這些硬件模塊可以操作無論是在串行或并行的方式,你可以構建過濾器基于帶寬和功率要求的最佳配置。例如,如果多個傳感器輸出需要被過濾,在FPGA既可以使用單獨的過濾器塊,每個傳感器(如果帶寬要求是足夠高),或使用一個單一過濾器塊和多個傳感器之間多路復用它(如果帶寬要求是足夠低)。

除了預處理原始傳感器數據時,FPGA還可以結合的讀數從多個傳感器,以智能的方式來進一步卸載的MCU處理要求。傳感器“融合”的算法,結合本地多個傳感器讀數,之前通知MCU的處理是必需的,可以顯著提高系統效率。結合心臟速率,溫度,以及排汗讀數和比對FPGA內部設置的警報水平的組合,例如,可以提供微控制器與不僅僅是原始數據更有價值的信息。

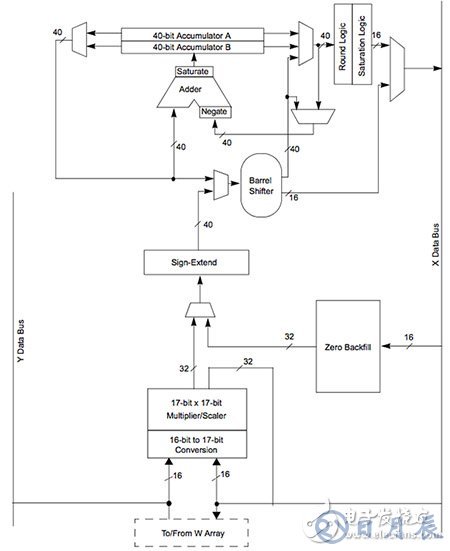

該MCU通常需要做一些數據的處理自己,但是。它不能放棄一切到FPGA中。幸運的是,即使是廉價的微控制器現在DSP的處理能力,并且可以有效地緊縮大量數據。久負盛名的Microchip的PIC MCU系列,例如,具有DSP的家庭成員,如DSPIC 33EP(如DSPIC33EP32MC202),在高達70 MIPS的操作與某些指令執行多達8個操作一次。過濾器的指令可以受益于40位累加器增加定點精度。在DSPIC33EP專用硬件DSP引擎的框圖如圖3所示。

框圖在Microchip的dsPIC33系列MCU

圖3:DSP引擎框圖在Microchip的dsPIC33系列MCU。 (Microchip的提供)

DSP引擎包括一個17×17乘法器/定標器零回填并簽署擴展到創建一個40位的結果。除法運算使用的是19次迭代一個重復循環通過一個單獨的硬件除法模塊實現的,且是可中斷降低最壞情況下的中斷延遲。桶式移位器有助于正確地調整數據為40位加法器和雙40位累加器。這種豐富的DSP的處理硬件除了常規的ALU,提供16位的加,減,和位操作。有了這個廣泛的集數據處理硬件,甚至復雜的操作都可以非常有效地支持。

的SoC FPGA的硬件加速和基于微控制器的處理

FPGA和微控制器做出這樣的好同伴的FPGA供應商甚至把MCU的同伴在其設備上。當這些系統級芯片(SoC)的FPGA用作同伴高端MCU的,更復雜的功能可以被移動到FPGA。一個常見的例子是用于FPGA來處置許多系統界面,不僅與標準外設還與外部存儲器。由于的SoC FPGA有顯著的片上存儲器,微控制器來管理數據緩沖和處理通信框架和外部存儲控制器,你有你需要實現一個完整的通信信道控制器,橋梁,或聚合碎片。這可以離開主MCU管理更高水平的功能,例如人機界面(HMI),過程控制,以及服務質量的優化。

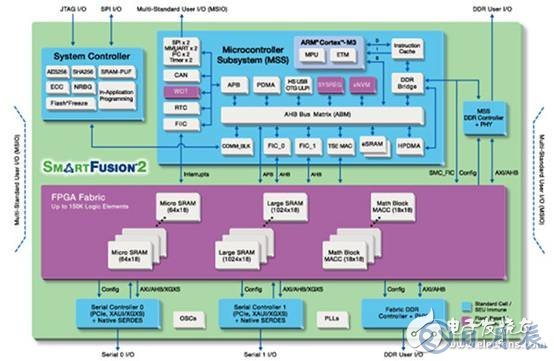

一些的SoC FPGA具有更多的功能,可從主機MCU卸載更是低層次處理。例如,Microsemi的SmartFusion2 SoC的FPGA系列(M2S050-FGG896的框圖如圖4所示),不僅擁有完整的ARM Cortex子系統,但其片上閃存NVM和SRAM塊顯著為MCU的一部分子系統。這些存儲器可以與處理器一起使用,作為代碼和數據存儲,與芯片外的DDR控制器作為大緩沖存儲器,并與PCIe和以太網控制器作為先進先出存儲。智能DMA控制器可以管理許多數據傳輸的不中斷的處理器。

Microsemi的SmartFusion2 SoC的FPGA的框圖

圖4:Microsemi的SmartFusion2 SoC的FPGA程序框圖。 (Microsemi公司提供)

SmartFusion2的SoC FPGA還具有片上硬件的安全性,可用于保護遠程代碼更新來自黑客和其他安全威脅。大型片上閃存可用于存儲受保護的引導代碼,這使得它可以支持安全啟動的操作,即使沒有本地安全功能的主機處理器。大量的可編程結構可以從主機控制器提供定制硬件加速,進一步卸載處理。例如,在一個底盤控制系統,可編程織物可以用于DSP的預處理傳感器數據,傳感器融合組合的電壓,電流,和溫度讀數,馬達控制的機箱風扇控制系統的溫度,控制臺接口,本地診斷監測和控制,或通過PCIe橋接至其他控制平面功能。隨著SoC的FPGA的同伴實際上可能承擔更多的處理比主機,切換一個MCU之間的傳統角色作為主角,并僅在次要輔助作用的FPGA。

結論

有許多應用,其中的MCU和一個FPGA,配對在一起,可以顯著地經由較低功耗,減少電路板空間,提高了處理,或增加的靈活性提高系統效率。了解如何通過分配這兩個設備之間的函數來實現其中的一些改進,可能是在你的下一個設計成功的關鍵。