在FPGA高速AD采集設(shè)計(jì)中,PCB布線差會(huì)產(chǎn)生干擾。今天小編為大家介紹一些布線解決方案。

1、信號(hào)線的等長(zhǎng)

以SDRAM或者DDRII為例,數(shù)據(jù)線,命令線,地址線以及時(shí)鐘線最好等長(zhǎng),誤差不要超過(guò)500mil。

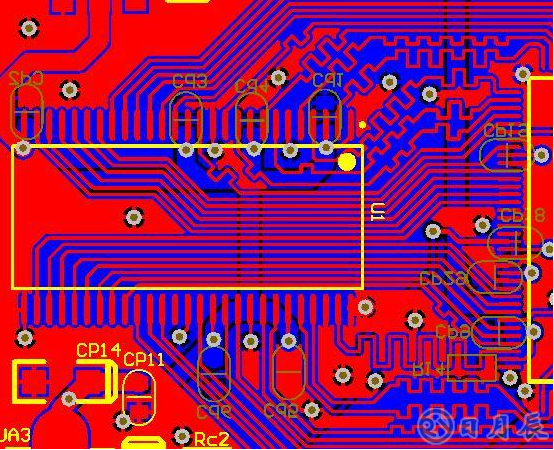

上圖是FPGA與SDRAM布線,時(shí)鐘頻率設(shè)定為125M,為了等長(zhǎng)可以走蛇形線。

蛇形走線雖然可以做到走線等長(zhǎng),但同時(shí)也占用更多的PCB面積。蛇形線沒(méi)有所謂濾波或抗干擾的能力,只可能降低信號(hào)質(zhì)量,所以只作時(shí)序匹配之用而無(wú)其它目的。

DDRII線路等長(zhǎng)設(shè)計(jì),最右邊的弧度較大的走線為差分的時(shí)鐘線,時(shí)鐘線質(zhì)量要求是比較高的。

布線是痛苦的,也是繁瑣的,布不通時(shí)需要重新布線,不厭其煩的嘗試,才能做出更好的效果。

2、電源芯片的選擇

很多高速AD場(chǎng)合,開(kāi)關(guān)電源并不合適,因?yàn)殚_(kāi)關(guān)電源帶來(lái)很多毛刺。大多數(shù)選擇線性穩(wěn)壓電源。小編以ASM1117為例為大家介紹電源芯片中電容的使用。

5V電源輸入端,應(yīng)加容值較大的鉭電容或者電解電容濾除電源的低頻噪聲,加104(0.1uF)瓷片電容濾除高頻噪聲。電源走線應(yīng)適當(dāng)加寬。

在PCB布線時(shí),也應(yīng)該在5V走線的末端加容值較大的電容。

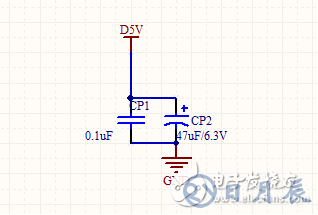

以ASM1117-3.3降壓為例,如下圖:

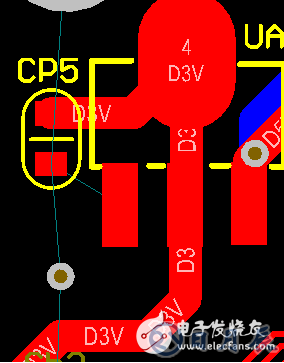

如上圖,1117的3.3輸出走線往下走,那么電容CP5放在旁邊是沒(méi)有任何效果的,通常這種電容是104瓷片電容,這個(gè)電容的容值是一個(gè)非常好的容值,在電源濾波中效果非常好。

那么該如何布局?

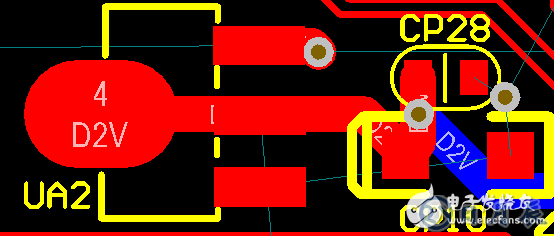

如上圖,此種布局,CP28以及 CP10放置,電容應(yīng)當(dāng)放在電源走線路徑上。注意電容不能離芯片引腳太遠(yuǎn),電容有濾波半徑,超出某一范圍,電容將起不到濾波效果。

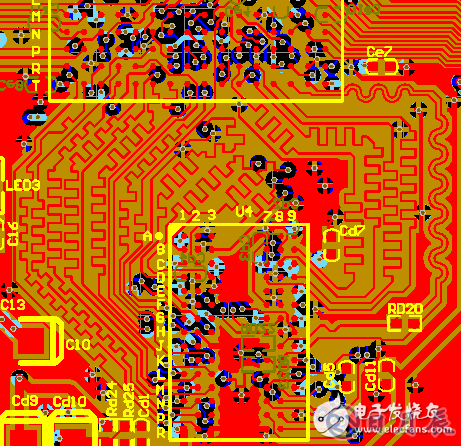

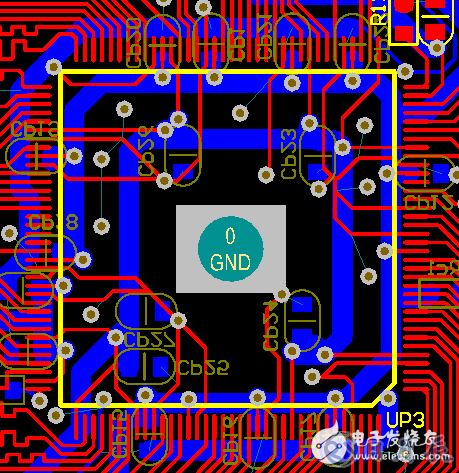

FPGA電源布線,根據(jù)多年布線經(jīng)驗(yàn)以及產(chǎn)品穩(wěn)定性,小編為大家推薦以下方案:

以QFP封裝的FPGA為例,有三種電源,1.2V,2.5V,3.3V。布線時(shí)最好如上圖效果,電源線之間最好隔開(kāi)距離,F(xiàn)PGA電源引腳要加入104電容。

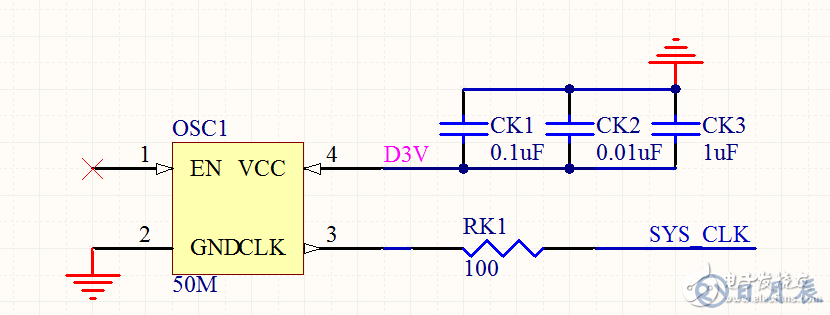

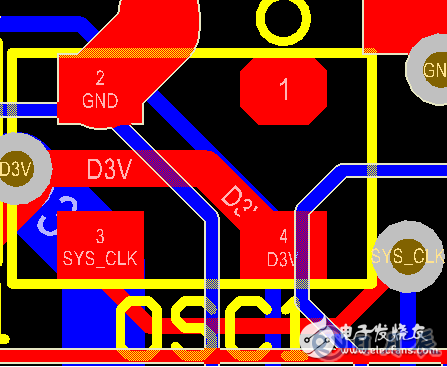

3、有源晶振布線

原理圖設(shè)計(jì)如上,時(shí)鐘輸出端串入100~330歐姆的電阻,防止阻抗不匹配時(shí)時(shí)鐘信號(hào)反射疊加。

有源晶振電源端加入103、104、105三種瓷片電容濾波,防止電源噪聲和時(shí)鐘之間的串?dāng)_。

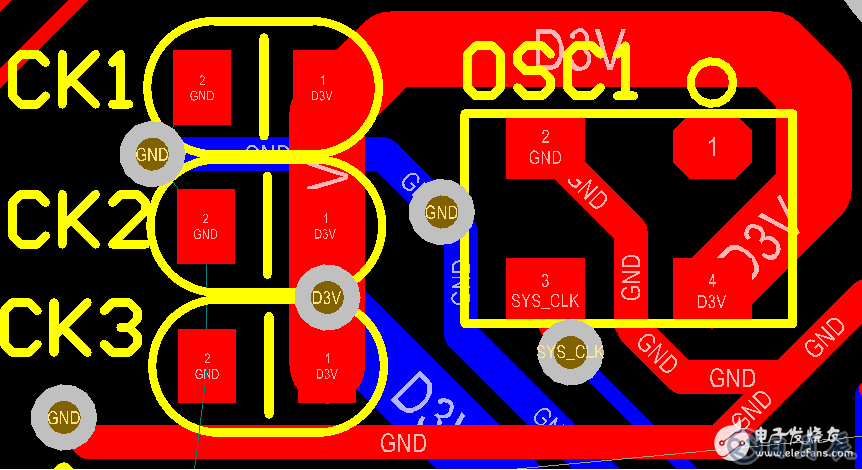

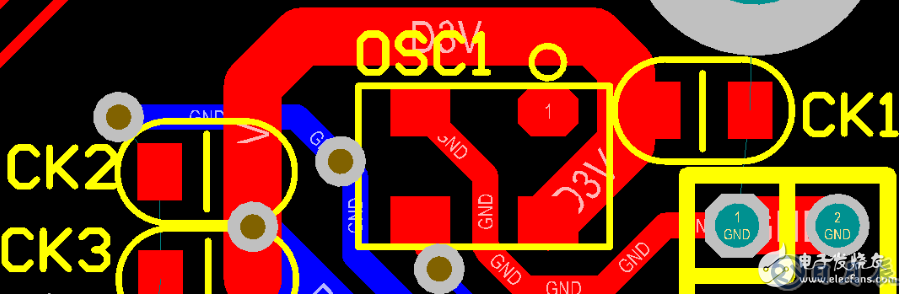

PCB布線時(shí),上述效果時(shí)很糟糕的。晶振下面不應(yīng)布線,電源走線應(yīng)遠(yuǎn)離時(shí)鐘線布線,并且中間加寬地線耦合,防止干擾。

如上圖布線,電源線避開(kāi)時(shí)鐘線,中間加入粗地線,注意有些地線不需要手動(dòng)連接,放置地過(guò)孔,在鋪銅(地網(wǎng)絡(luò))時(shí),會(huì)自動(dòng)加入。

此種方式放置電容亦可行。