電流檢測(cè)電阻有多種形狀和尺寸可供選擇,用于測(cè)量諸多汽車、功率控制和工業(yè)系統(tǒng)中的電流。使用極低值電阻(幾 m?或以下)時(shí),焊料的電阻將在檢測(cè)元件電阻中占據(jù)很大比例,結(jié)果大幅增加測(cè)量誤差。高精度應(yīng)用通常使用 4 引腳電阻和開爾文檢測(cè)技術(shù)以減少這種誤差,但是這些專用電阻卻可能十分昂貴。另外,在測(cè)量大電流時(shí),電阻焊盤的尺寸和設(shè)計(jì)在確定檢測(cè)精度方面起著關(guān)鍵作用。本文將描述一種替代方案,該方案采用一種標(biāo)準(zhǔn)的低成本雙焊盤檢測(cè)電阻(4 焊盤布局)以實(shí)現(xiàn)高精度開爾文檢測(cè)。圖 1 所示為用于確定五種不同布局所致誤差的測(cè)試板。

電流檢測(cè)電阻

采用 2512 封裝的常用電流檢測(cè)電阻的電阻值最低可達(dá) 0.5m?,其最大功耗可能達(dá) 3 W。為了展現(xiàn)最差條件下的誤差,這些試驗(yàn)采用一個(gè) 0.5 m?、3 W電阻,其容差為 1%(型號(hào):ULRG3-2512-0M50-FLFSLT;制造商:Welwyn/TTelectronics)。

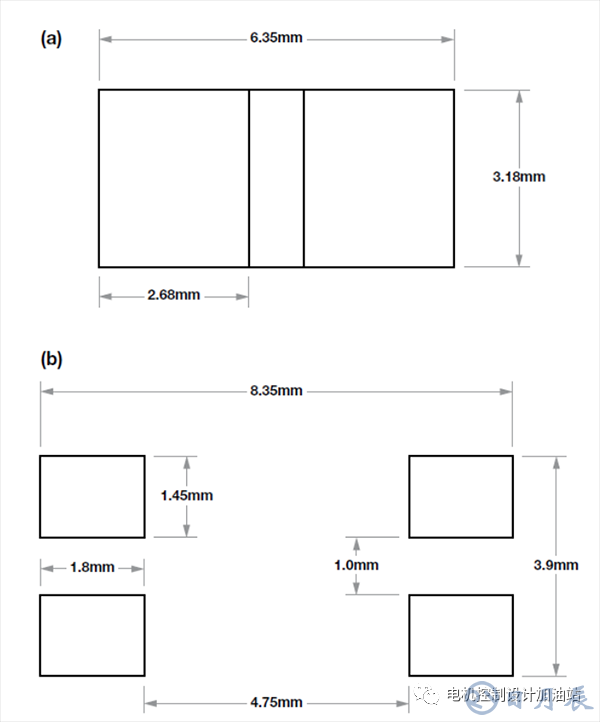

其尺寸和標(biāo)準(zhǔn) 4 線封裝如圖 2 所示。

傳統(tǒng)封裝

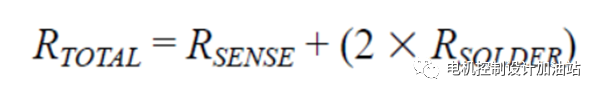

對(duì)于開爾文檢測(cè),必須將標(biāo)準(zhǔn)雙線封裝焊盤進(jìn)行拆分,以便為系統(tǒng)電流和檢測(cè)電流提供獨(dú)立的路徑。圖 3 顯示了此類布局的一個(gè)例子。系統(tǒng)電流用紅色箭頭表示的路徑。如果使用一種簡(jiǎn)單的雙焊盤布局,則總電阻為:

為了避免增加電阻,需要把電壓檢測(cè)走線正確的布局到檢測(cè)電阻焊盤處。系統(tǒng)電流將在上部焊點(diǎn)導(dǎo)致顯著的壓降,但檢測(cè)電流則會(huì)在下部焊點(diǎn)導(dǎo)致可以忽略不計(jì)的壓降。可見,這種焊盤分離方案可以消除測(cè)量中的焊點(diǎn)電阻,從而提高系統(tǒng)的總體精度。

優(yōu)化開爾文封裝

圖 3 所示布局是對(duì)標(biāo)準(zhǔn)雙焊盤方案的一種顯著的改進(jìn),但是,在使用極低值電阻(0.5 m? 或以下)時(shí),焊盤上檢測(cè)點(diǎn)的物理位置以及流經(jīng)電阻的電流對(duì)稱性的影響將變得更加顯著。例如,ULRG3-2512-0M50-FLFSL 是一款固態(tài)金屬合金電阻,因此,電阻沿著焊盤每延伸一毫米,結(jié)果都會(huì)影響有效電阻。使用校準(zhǔn)電流,通過比較五種定制封裝下的壓降,可以確定最佳檢測(cè)布局。

測(cè)試PCB板

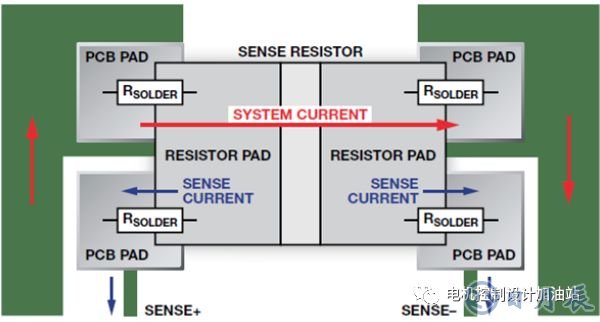

圖 4 展示在測(cè)試 PCB 板上構(gòu)建的五種布局模式,分別標(biāo)記為 A到 E。我們盡可能把走線布局到沿著檢測(cè)焊盤延伸的不同位置的測(cè)試點(diǎn),表示為圖中的彩點(diǎn)。各個(gè)電阻封裝為:

A. 基于 2512 建議封裝的標(biāo)準(zhǔn) 4 線電阻(見圖 2(b))。檢測(cè)點(diǎn)對(duì)(X 和 Y)位于焊盤外緣和內(nèi)緣(x 軸)。B. 類似于 A,但焊盤向內(nèi)延伸較長(zhǎng),以便更好地覆蓋焊盤區(qū)(見圖 2(a))。檢測(cè)點(diǎn)位于焊盤中心和末端。C. 利用焊盤兩側(cè)以提供更對(duì)稱的系統(tǒng)電流通路。同時(shí)把檢測(cè)點(diǎn)移動(dòng)到更中心的位置。檢測(cè)點(diǎn)位于焊盤中心和末端。D. 與 C 類似,只是系統(tǒng)電流焊盤在最靠里的點(diǎn)接合。只使用了外部檢測(cè)點(diǎn)。E. A 和 B 的混合體。系統(tǒng)電流流過較寬的焊盤,檢測(cè)電流流過較小的焊盤。檢測(cè)點(diǎn)位于焊盤的外緣和內(nèi)緣。

在模板上涂抹焊料,并在回流爐中使用回流焊接。使用的是ULRG3-2512-0M50-FLFSLT 電阻。

測(cè)試步驟

測(cè)試設(shè)計(jì)如圖 5 所示。使 20 A 的校準(zhǔn)電流通過各個(gè)電阻,同時(shí)使電阻保持在 25°C。在加載電流后 1 秒內(nèi),測(cè)量產(chǎn)生的差分電壓,以防止電阻溫度升高 1°C 以上。同時(shí)監(jiān)控各個(gè)電阻的溫度,以確保測(cè)試結(jié)果均在 25°C 下測(cè)得。電流為 20 A 時(shí),通過 0.5 m? 電阻的理想壓降為 10 mV。

測(cè)試結(jié)果

表 1 列出了采用圖 4 所示檢測(cè)焊盤位置測(cè)得的數(shù)據(jù)。

表 1. 測(cè)得電壓和誤差

*無開爾文檢測(cè)。對(duì)通過高電流主焊盤的電壓進(jìn)行測(cè)量,以展示與焊料電阻相關(guān)的誤差。

觀察結(jié)果

1. 由于結(jié)果的可比較性以及各電阻偏差都在容限范圍之內(nèi),所以得出封裝 C 和 D 的誤差最少。封裝 C 為首選封裝,因?yàn)樗淮罂赡軐?dǎo)致與元件放置容限相關(guān)的問題。2. 在每一種情況下,電阻外端的檢測(cè)點(diǎn)提供的結(jié)果最準(zhǔn)確。這表明,這些電阻是制造商根據(jù)電阻的總長(zhǎng)度設(shè)計(jì)的。3. 請(qǐng)注意,在未使用開爾文檢測(cè)時(shí),焊料電阻相關(guān)誤差是 22%。這相當(dāng)于約 0.144 m? 的焊料電阻。4. 封裝 E 展示了不對(duì)稱焊盤布局的效應(yīng)。回流期間,元件通過大量焊料才能焊盤。應(yīng)避免這種封裝。

結(jié)論

根據(jù)前面所示結(jié)果,最佳封裝是 C,其預(yù)期測(cè)量誤差小于 1%。該封裝的建議尺寸如圖 6 所示。

Analog Dialogue 46-06 Back Burner, June (2012) 3檢測(cè)走線的布局也會(huì)影響測(cè)量精度。為了實(shí)現(xiàn)最高精度,應(yīng)在電阻邊緣測(cè)量檢測(cè)電壓。圖 7 所示建議布局采用通孔,把焊盤外邊緣布局到另一層,從而避免切割主電源層。

本文中的數(shù)據(jù)可能并不適用于所有電阻,而且結(jié)果可能因情況而異,具體取決于電阻的材質(zhì)和尺寸。應(yīng)該咨詢電阻制造商。用戶有責(zé)任確保封裝的布局尺寸和結(jié)構(gòu)均符合各項(xiàng) SMT制造要求。對(duì)于因使用本封裝而可能導(dǎo)致的任何問題,ADI概不負(fù)責(zé)。