ADC在實際應用中,經常會出現無法達到標稱精度的情況,而且還會出現波形嚴重失真的問題,這一現象長期困擾著我們的硬件工程師,那么,在實際的ADC應用中,為何會出現這種情況呢?

筆者在這里通過一個實例和大家一起共同來探討 ADC在應用中可能會碰到的問題。

案例分享

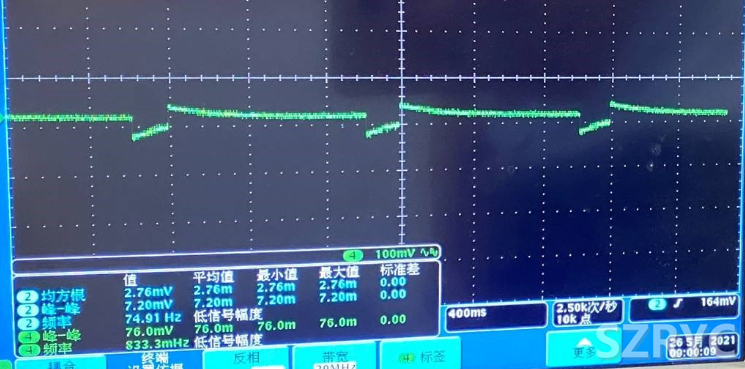

日前,有客戶公司在用某ADC做AD轉換的時候,碰到這樣一個問題,客戶傳感器型號pt100,在采集信號時,輸入采樣端的波形如下:

我們首先假定這是一個直流前端,拋開交流耦合等因素,單從這個采樣波形來看,采樣端明顯是工作異常的。那么,為何會出現這種情況呢?

ADC模型初探

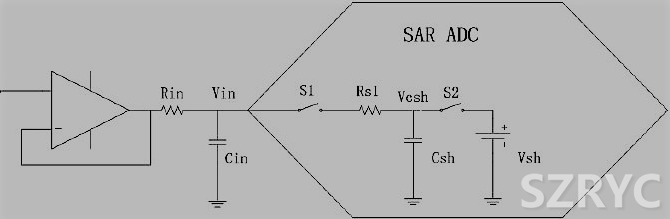

我們先來大致解剖一下 ADC電路參考模型及其驅動電路,通過這個模型來跟大家共同來探討一番,為了便于做定量分析,我們在文中插入一些公式,供大家參考。

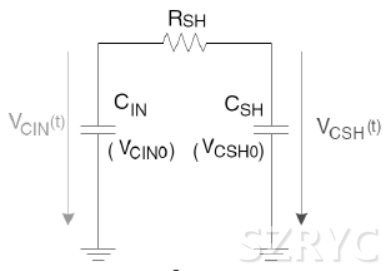

為了更加直觀,我們刪繁就簡,重新整理這個電路,單看輸入、采樣端的電路模型,大致如下:

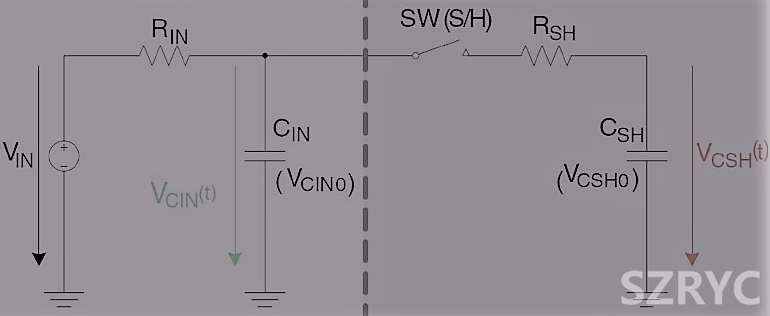

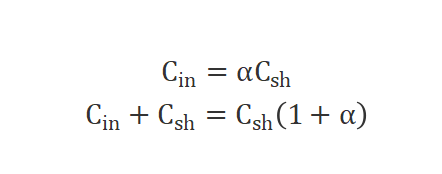

為了簡化設計,我們假設輸入電壓近似于一個直流電源,拋開耦合因素,輸入內阻遠大于采樣電阻,Rin>>Rsh,輸入電容和采樣電容之間的關系用a來表示:

初始狀態,相對來說Vin向Cin充電相對較小,主要看Cin向Csh充電過程,我們構建電路模型如下圖所示:

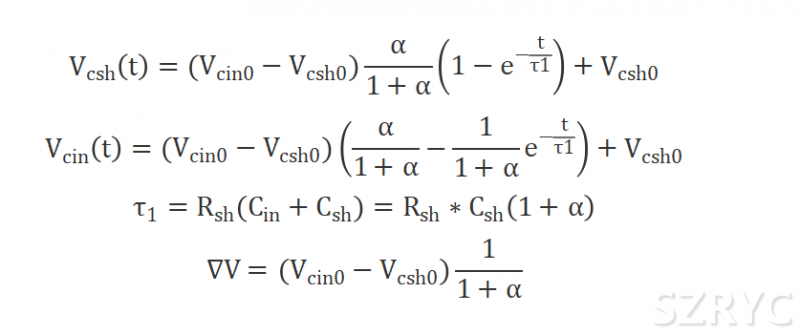

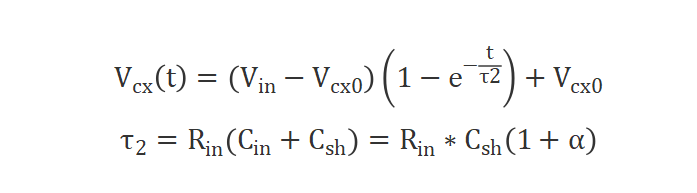

根據以上模型,可以大致推導出第1階段輸入電壓和采樣電壓對應方程,以及采樣電容充電時間關系。

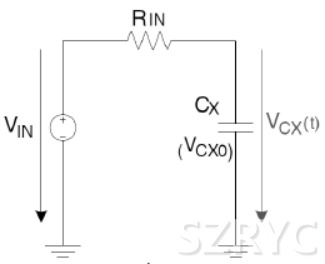

當Csh電壓迅速上升到與Cin相當之后,我們忽略Rsh對電路的影響,我們重新構建第2階段電路模型如下。

此時,等效電容為輸入電容和采樣電容并聯,根據以上模型,可以大致推導出輸入電壓和采樣電壓對應方程如下:

此時,根據等效模型,我們可以推導出正常狀態下:

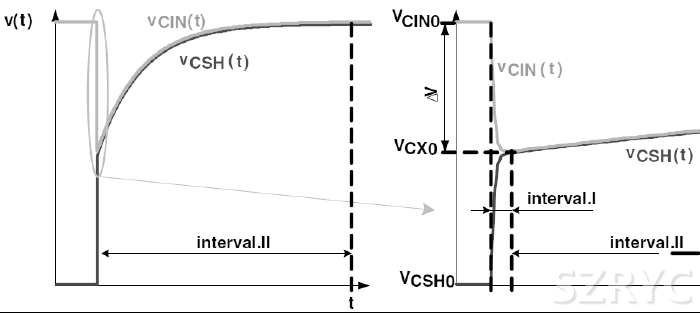

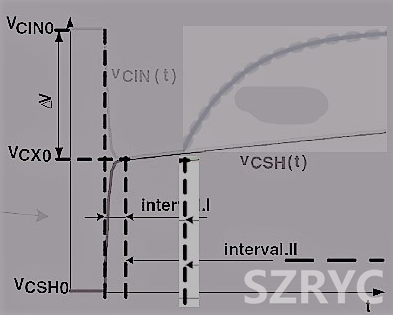

由此,我們可以畫出采樣端波形大致如下:

根據ADC內部結構和,我們可以很輕松的推導出,第二階段的時間遠遠大于第一階段的時間,同時,我們也可以推導出,采樣時間和輸入電阻必須滿足:

按照正常采樣,第二階段采樣時間必須要滿足輸入電阻、輸入電容和采樣電容并聯的乘積關系。如果采樣不足,又會出現怎樣的情況呢?在采樣開關斷開之后,采樣保持階段,由于Cx變小,輸入電容充電速度明顯加快,此時,Csh電壓幾乎不變,大致波形應如下(具體推導公式不再列出):

結合該客戶反饋的測試結果,我們大致判斷出,客戶這個問題是由于在未達到采樣條件時就開始進行ADC采樣并轉換引起。

解決方案

結合上述電路模型及其推導公式,我們該如何解決此類問題呢?我們給出三種建議:

A.延遲采樣時間;

B.加大輸入電容;

C.增加驅動電路,重構輸入阻抗。

實施細節

一、延遲采樣,增加采樣周期

這一點不難理解,只要采樣速率沒有要求,理論上來說,增加采樣周期,完成ADC轉換完全沒問題,本文不做重點講解。

二、加大輸入電容

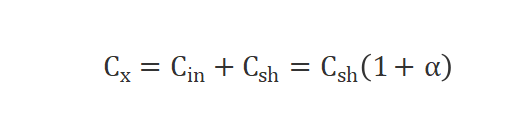

我們在很多ADC采樣場合都看到ADC輸入前端有一個電容,如果我們設定Rin非常小,忽略不計,那么這個電容有何作用呢?本文中,我們有一個推導公式:

由于在每個采樣周期內,輸入電容和采樣電容的電壓值都會相對固定,如果我們通過調整輸入輸入電容和采樣電容的比值來調整第一階段的快速充電時間,這似乎不失為一個好辦法。

但是,當輸入電源發生變化的時候,由于采樣電容吸收能力有限,采樣端輸入電容泄放又會遇到新的難題。同時,對于高頻信號來說,電容越大,等效阻抗會更小。

所以,在采樣端引入輸入電容的時候,我們需要非常謹慎,這個電容大多數是用來做高頻分量濾波用的。

三、增加驅動能力,重構輸入阻抗

我們再回到第2階段采樣時間這個公式:

![]()

如果我們能夠降低輸入阻抗,就會大大縮短采樣時間,目前增加驅動有兩種主流方法:

第一種是用變壓器來做驅動電路,這個方法有一個弱點,只能針對交流信號,對工作頻率有要求,需要做匹配設計。

另一種方法是用運放做跟隨器,這樣可以大大降低信號端的內阻,大多數模擬前端都采用這種方法來做前端設計。

經過和客戶確認,客戶后來采用運放做跟隨驅動的方法,重新測試一版,測試采樣端波形如下圖,從硬件電路來看,應該找到問題所在,目前還在驗證中。