1 、引言

led 顯示屏具有亮度高, 故障低、能耗少、使用壽命長、顯示內容多樣、顯示方式豐富等優點, 可廣泛用于公路、金融、證券、車站、碼頭、體育場館等公共場合, 其顯示數據通常來自上位PC 機, 這就要求有一個高速通道來傳輸大量的顯示數據,USB2. 0 接口無疑是一個很好的解決方案。USB 由總線提供電源, 傳輸時具有CRC 檢錯、糾錯能力, 能實現真正的實時熱插拔, 并支持多個外設連接到同一個連接器上, 從而緩解PC 系統資源沖突, 這些突出的優點使得USB1. x 在PC 機外部設備上得到了廣泛的應用, USB2. 0 傳輸速度高達480Mb/ s ,是USB1. x 的40 倍, 并向下兼容USB1. x。這樣就使得快速大量的數據傳輸得以實現。

2 、CY7C68013 簡述

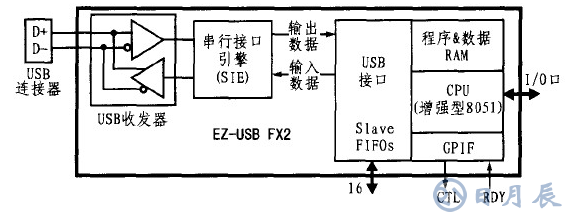

帶高速Slave FIFO 通用外部接口的CY7C68013是CYPRESS 公司推出的USB2. 0 集成微處理芯片,片上集成了USB 收發器(SIE) 、增強型8051 單片機(其指令系統與普通8051 單片機完全兼容) 及8k 程序存儲區, 共有4 個支持USB2. 0 高速傳輸的“大”端點(2 個IN 端點和2 個OUT端點) 和4kB 片內RAM,該RAM可配置為4 個“大”端點的FIFO ,其中2 個“大”端點可以配置為雙、三、四緩沖區( FIFO) ,一個“大”端點最大可配置為2kB FIFO ,更重要的是,該芯片提供了兩個用于實現USB2. 0 高速傳輸的可編程外部設備接口以及Slave FIFO 和GPIF , 這2 個通用外部接口可通過與4 個“大”端點協調工作來實現USB2. 0 的高速傳輸, 本文只討論Slave FIFO 可編程外部設備接口的應用。

CY7C68013 有56pin、100pin、128pin 三種封裝,其中56pin 已具備所有USB2. 0 功能, 而100pin 則在56pin 基礎上增加了更多I/ O 和更多GPIF 模式下的控制信號, 128pin 又在100pin 基礎上增加了用于擴充數據存儲區的地址總線和數據總線。本應用就是基于可編程外部設備接口Slave FIFO , 大量數據傳輸可直接由FPGA 處理而無需擴充外部數據存儲區,在此選擇最經濟的56pin CY7C68013 即可滿足設計要求, 其體系結構如圖1 所示。

圖1 56 腳CY7C68013 的體系結構

3、硬件設計

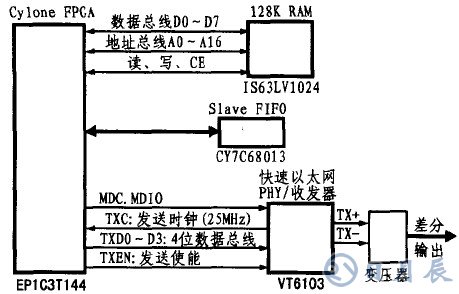

圖2 所示是FPGA 與CY7C68013 的連接圖, 除將IFCLK作為FPGA 輸入時鐘外,其它信號均在FP2GA 和CY7C68013 之間互連。由于FPGA 片內RAM很小, 本系統還使用了一片128k ×8 的高速靜態RAM(型號為IS63LV1024 , 讀寫周期為15ns) 作為數據暫存器。FPGA 與CY7C68013、RAM、VT6103 的硬件連接見圖2。

圖2 硬件連接總圖

從USB 收到的來自上位PC 機數據最終將被遠端安裝在LED 顯示屏屏體內的顯示控制部件中, 當RAM被填入預定數量的顯示數據時, FPGA 會從RAM中連續取出數據并送到與VT6103 連接的4 位數據輸出端口, VT6103 收到4 位數據后, 其內部會自動按照IEEE802. 3 規范對該數據進行4B5B(轉換4 位數據數據碼為5 位數據碼) 重新編碼,然后將5B碼送擾頻器,再經片內整形后輸出給以太網變壓器,以驅動五類雙絞線并將數據傳給遠端顯示控制部件。

4、軟件設計

本系統的外部主設備接口邏輯采用VHDL 硬件描述語言,利用ALTERA 公司QUARTUSII 開發平臺進行設計。軟件設計是以FPGA 為核心的,主要由下面3 個并行執行的部分組成, 在此每個部分分別設計為一個VHDL 進程(process) :

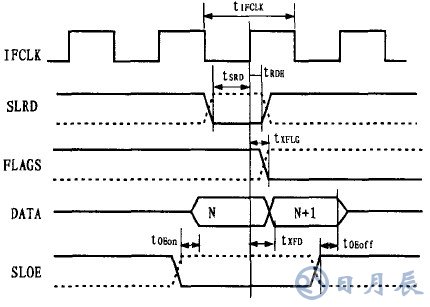

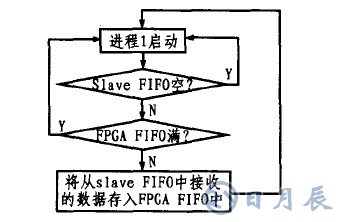

進程1 : 外部主設備FPGA 同步讀寫CY7C68013“大”端點FIFO 的時序邏輯, 并把接收到的數據存入FPGA FIFO 中。這部分只需要根據Slave FIFO 讀寫時序進行設計,Slave FIFO 時序圖如圖3 所示。

圖3 Slave FIFO 同步讀時序

這里需要引起注意的是兩個建立時間: 其一是tOEon , 這個建立時間是從SLOE 拉低到Slave FIFO 數據有效。其二是tSRD ,即從SLRD 信號拉低到第1 個同步讀時鐘上升沿的時間。這兩個建立時間應大于等于CY7C68013 數據手冊規定的時間。由于該FPGA有59904 bit 的片上RAM, 這里使用其中4k byte 的RAM來生成FIFO 結構,這樣從Slave FIFO 同步接收到的USB 數據就可以直接存入FPGA 片上的4k FI2FO 中。圖4 是此進程的設計流程圖。

圖4 進程1 設計流程

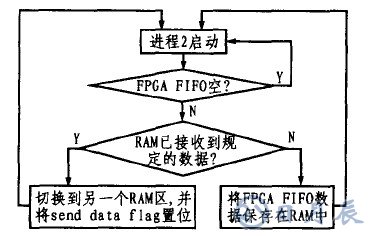

進程2 : 用于完成將FPGA 的FIFO 中數據寫入128kB RAM的設計。只要FPGA 的FIFO 中有數據,則該進程啟動, FPGA 會連續地把片內FIFO 中取出的數據存入片外128kB 的高速靜態RAM( IS63LV1024) 中, 這個片外的128kB RAM分為兩個64kB 區,兩個區輪流接收來自FPGA 片內FIFO 的數據, 當一個區接收完規定的顯示數據后, FPGA 會置位send data flag 去啟動進程3 ,如果FPGA 片內FIFO中還有數據, 則FPGA 會把RAM切換到另一個區繼續接收片內FIFO 中的數據,其設計流程圖如圖5 所示。

圖5 進程2 設計流程

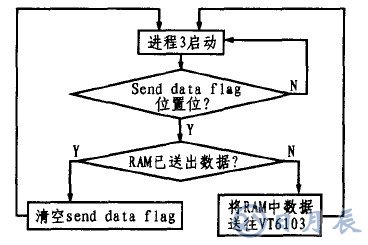

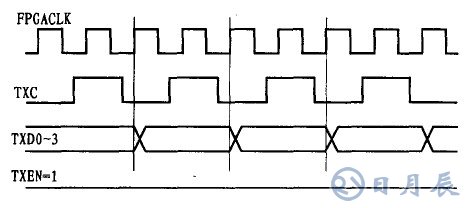

進程3 : 此進程由send data flag 信號啟動, 當發送數據標志被置位時, 此進程啟動。此后, FPGA 開始從已完成顯示數據接收的RAM區讀取數據并送到4 位寬度的數據輸出口, 此輸出口與VT6103 相連。VT6103 以25MHz 時鐘每次接收半個字節(4bit) ,然后經片內4B5B 編碼、整形后將數據由差分輸出口TX+ 和TX- 串行輸出, 以把數據從USB2. 0 接口模塊發給外部的顯示處理模塊。其設計流程圖如圖6所示。其中, VT6103 接收顯示數據時序如圖7 所示。每次接收4bit 后, 芯片內部都將自動對每次接收到的4bit 數據進行處理并以100MHz 的時鐘頻率串行差分輸出給以太網變壓器。

圖6 進程3 設計流程

圖7 接收顯示數據時序