1 引言

隨著科學(xué)技術(shù)的不斷發(fā)展,列車也向著高速發(fā)展,列車車載系統(tǒng)中逐步采用高速數(shù)字電路。在列車上有許多干擾源,包括各類變壓器、風(fēng)機(jī)、受電弓、空氣壓縮機(jī)等產(chǎn)生的電磁干擾,影響著列車內(nèi)高速數(shù)字電路的正常工作。此外,為保證乘車環(huán)境和工作環(huán)境的舒適,車上還配備有空調(diào)、電熱器、通風(fēng)機(jī)等各類電器設(shè)備,他們同樣對(duì)外產(chǎn)生著電磁輻射,影響到高速數(shù)字電路的正常工作。因此,在列車上如此復(fù)雜的環(huán)境中,如何確保高速數(shù)字信號(hào)的可靠,將變得尤為重要。這些問(wèn)題如果不處理好將導(dǎo)致信號(hào)失真,時(shí)序錯(cuò)誤,系統(tǒng)不穩(wěn)定等諸多情況, 會(huì)帶來(lái)不可估計(jì)的損失。

為保證列車通信、控制等系統(tǒng)的正常運(yùn)行, 設(shè)備的抗干擾設(shè)計(jì)與功能設(shè)計(jì)同樣重要。在設(shè)計(jì)初必須考慮數(shù)字電路干擾的抑制問(wèn)題, 否則很難達(dá)到高速數(shù)字電路抗干擾要求。因此首先應(yīng)當(dāng)提高數(shù)字電路板的抗干擾能力及減小電路輻射, 避免在設(shè)計(jì)完成之后再去進(jìn)行電路板的抗干擾的補(bǔ)救措施。

2 干擾形成方式

干擾形成的三個(gè)基本方式: 干擾源、耦合途徑、敏感源。下面分別從這幾個(gè)方面進(jìn)行闡述。

2.1 PCB電路板干擾耦合途徑

PCB 電路板上干擾主要有共模干擾和差模干擾。差模干擾是由信號(hào)回路產(chǎn)生的,共模干擾是由電纜上的共模電流產(chǎn)生。對(duì)于印制電路板主要指其差模干擾,因?yàn)槠洳钅8蓴_的頻率范圍為電路信號(hào)所占有的整個(gè)頻段,不僅能通過(guò)其導(dǎo)線耦合到各敏感源器件,同時(shí)電流環(huán)還會(huì)耦合進(jìn)外部產(chǎn)生的各類干擾,影響正常的工作系統(tǒng)。減小差模干擾的主要方法是布線時(shí)盡量減短走線長(zhǎng)度, 減小信號(hào)環(huán)路面積。

2.2 PCB電路板上干擾源產(chǎn)生方式

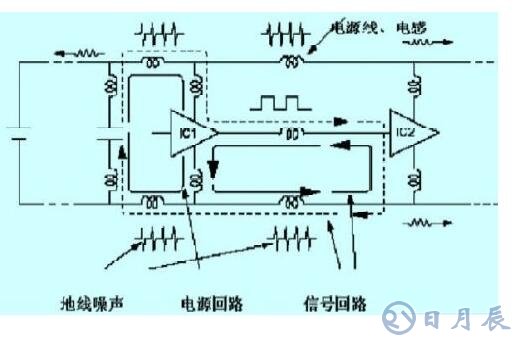

高速數(shù)字電路各類干擾的主要產(chǎn)生原因是由電源自身固有噪聲頻率及外部線路上各類變化的di/dt、du/dt 產(chǎn)生,由于電路板上存在電源回路、信號(hào)回路、高速信號(hào)回路及附屬在線路上的各類容性、感性負(fù)載,因此當(dāng)信號(hào)產(chǎn)生跳變時(shí)都將產(chǎn)生一個(gè)尖峰沖擊形成噪聲,而這些噪聲將通過(guò)各回路的電流環(huán)沿路傳導(dǎo),因此應(yīng)當(dāng)抑制電源自身的固有噪聲及各種高速數(shù)字跳變引起的噪聲。 抑制電路自身或者各類突變信號(hào)產(chǎn)生的噪聲,最好的抑制方式就是去耦和濾波。這樣既減少了自身的噪聲也能夠吸收外部對(duì)其的影響,提高自身的抗干擾能力。圖1 簡(jiǎn)要說(shuō)明在各個(gè)電路階段所產(chǎn)生的噪聲。

圖1 各個(gè)電路階段噪聲的產(chǎn)生

2.3 PCB電路板上的敏感源

對(duì)于高速數(shù)字信號(hào)敏感源主要是指容易受到外部干擾的對(duì)象,例如:A/D、D/A 變換器,邏輯控制器,單片機(jī),晶振,數(shù)字IC,弱信號(hào)放大器等。這些器件的穩(wěn)定性直接關(guān)系到電路板的系統(tǒng)工作的穩(wěn)定性和工作精度,因此對(duì)于這些敏感源要做好相應(yīng)的保護(hù), 提高自身的抗干擾能力。

3 提高PCB 線路板抗干擾措施

3.1 減小耦合回路

減小耦合的主要方法是減小信號(hào)環(huán)路面積, 其中主要應(yīng)該解決地線、電源、敏感信號(hào)源及板邊的環(huán)路面積。

3.1.1 減小地線、電源耦合回路

地線阻抗是造成線路板上地線噪聲的主要原因, 因此應(yīng)該盡量減小地線阻抗, 可以采取地平面或網(wǎng)格地。

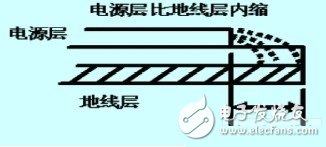

對(duì)于高速數(shù)字電路板應(yīng)該采用多層板, 以減小環(huán)路面積, 將中間層作為電源或地層, 并且盡量保證電源與地相鄰的層間距盡量小;讓每一信號(hào)層都有一對(duì)應(yīng)的地線層, 信號(hào)線與其地回路構(gòu)成的環(huán)面積要盡可能小, 環(huán)面積越小, 對(duì)外的干擾越少。針對(duì)這一特點(diǎn), 在地平面分割時(shí), 要考慮到地平面與重要信號(hào)走線的分布, 防止由于地平面開(kāi)槽等帶來(lái)的問(wèn)題,信號(hào)線不能跨越地平面和電源平面分隔區(qū), 防止形成大的地線回路。同時(shí)電源層應(yīng)該比地線層內(nèi)縮3 m m 左右的距離, 這樣將能夠抑制70% 以上的電源干擾。如圖2 所示。

圖2 電源層比地線層內(nèi)縮示意圖

3.1.2 減小敏感源信號(hào)的耦合回路

對(duì)于敏感信號(hào)例如: 周期性信號(hào), 如時(shí)鐘信號(hào)、模擬信號(hào)、地址總線的低位信號(hào)等產(chǎn)生干擾較強(qiáng), 也是設(shè)計(jì)高速數(shù)字電路的關(guān)鍵所在。印制板上關(guān)鍵信號(hào)布線應(yīng)該按照從高到低的原則走線(排序方式:高到低 :模擬信號(hào)-復(fù)位信號(hào)-I2C- 時(shí)鐘信號(hào)- 讀寫信號(hào)- 高速、射頻信號(hào)- 數(shù)據(jù)總線- 地址總線);關(guān)鍵信號(hào)布線盡量走內(nèi)層;并要配小電容并聯(lián)進(jìn)行濾波;信號(hào)層只有通過(guò)地平面隔離后的兩個(gè)層, 才可以平行走線; 信號(hào)線應(yīng)盡可能使其互連線最短; 印制板上高頻連線的元件盡可能靠近走線短; 以減少高頻信號(hào)的分布參數(shù)和電磁干擾, 這樣才能夠提高敏感信號(hào)源的抗干擾能力。

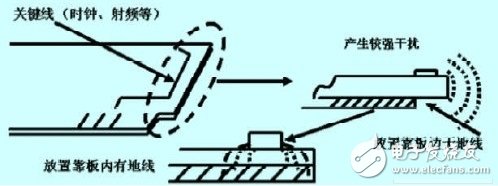

3.1.3 減小線路板邊緣的耦合回路

印制電路板的板邊處理是否合理, 決定著是否能夠更加有效地抑制信號(hào)的對(duì)外干擾。為防止高速數(shù)字電路通過(guò)板邊對(duì)外干擾, 應(yīng)該嚴(yán)格控制其布線位置, 讓其盡量靠近印制板內(nèi)部。高頻等干擾較強(qiáng)信號(hào)線不應(yīng)該走到板的邊緣, 以防止無(wú)對(duì)應(yīng)地層耦合回路, 產(chǎn)生信號(hào)對(duì)外的干擾泄漏, 如圖3 所示:

圖3 線路板邊的耦合回路

3.2 抑制干擾源

抑制干擾源就是盡可能地減小干擾源du/dt、di/dt產(chǎn)生的影響。減小干擾源du/dt 主要通過(guò)在干擾源兩端并聯(lián)電容,增加去耦和濾波實(shí)現(xiàn)。減小干擾源di/dt 主要通過(guò)在干擾源中串聯(lián)電感或增加續(xù)流二極管來(lái)實(shí)現(xiàn),例如:在繼電器中增加續(xù)流二極管,能夠消除斷開(kāi)線圈時(shí)產(chǎn)生的反電動(dòng)勢(shì)干擾。

3.2.1 增加去耦電容

去耦電容是把輸出信號(hào)的干擾作為濾除對(duì)象。在芯片附加并聯(lián)去耦電容就可以消除電源自激及抑制電平變化的沖擊,能夠讓電源噪聲及電平變化的沖擊以最短的路徑回流到地線, 增加抗干擾能力。為了很好地抑制噪聲,應(yīng)盡可能為每一芯片配備去耦電容,并且去耦電容盡量靠近芯片電源和地管腳擺放。去耦電容的取值一般為0.01-0.1uf,可以按照C=1/F,既10MHZ 取0.1uf,100MHZ 取0.01uf,頻率越高,去耦電容取值應(yīng)該越小。

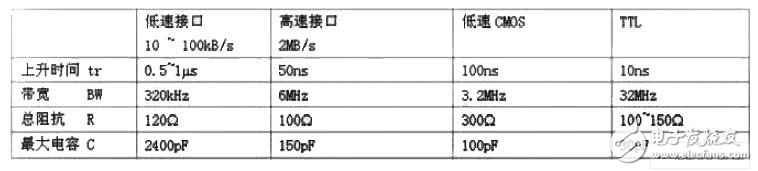

3.2.2 電路濾波吸收

對(duì)于容易產(chǎn)生毛刺的突變信號(hào)應(yīng)該采取相應(yīng)的濾波形式, 抑制高速信號(hào)的突變產(chǎn)生的高頻毛刺。濾波的方法一般采用無(wú)源元件電容或電感配合電阻, 利用其對(duì)電壓、電流的儲(chǔ)能特性達(dá)到濾波的目的。常采用RC 濾波電路,當(dāng)電壓突然升高時(shí),并聯(lián)電容C 能夠儲(chǔ)存能量,而當(dāng)電壓下降時(shí)釋放能量, 從而使負(fù)載濾波后電壓比較平滑, 減少高頻噪聲。但為了不影響正常的高頻信號(hào)波形,也不能取值太大,盡量使用小電容。根據(jù)電路的總阻抗及高頻信號(hào)的帶寬、上升時(shí)間、根據(jù)計(jì)算及經(jīng)驗(yàn)得出濾波電容C 的選擇大小參考下表1:系統(tǒng)工作頻率越高使用濾波電容取值應(yīng)該越小。

表1 各種情況下濾波電容的選取

4 結(jié)束語(yǔ)

高速數(shù)字電路的抗干擾設(shè)計(jì)的可靠性對(duì)整個(gè)電子、電氣設(shè)備的整體性能有著深遠(yuǎn)的影響, 任何產(chǎn)品的可靠性應(yīng)從設(shè)計(jì)的源頭抓起, 只有切實(shí)把握印制電路的可靠性設(shè)計(jì)才能保證產(chǎn)品的可靠性, 真正提升印制板的可靠性能。

通過(guò)各類圖示能夠看出按照方法改進(jìn)后的高速數(shù)字印制電路板能夠減小自身產(chǎn)生的噪聲, 同時(shí)提高自身的抗干擾能力。從研發(fā)成本的經(jīng)濟(jì)考慮, 在設(shè)計(jì)初期考慮電路的抗干擾問(wèn)題將能夠節(jié)約大量重復(fù)設(shè)計(jì)費(fèi)用。此方法在時(shí)代電氣公司技術(shù)中心內(nèi)部推廣取得了很好的實(shí)踐效果, 提高單板一次性成功概率, 既節(jié)約設(shè)計(jì)成本, 也提高了設(shè)計(jì)效率。