如今,電子行業發展速度令人瞠舌,5G、AI、工業4.0、智能汽車一波又一波的應用革新引領了“新浪潮”,但隨之帶來的就是巨量的計算、分析、處理量。數據顯示,2019年數據總量將達40ZB總量,如此龐大的潛在計算量,FPGA的小尺寸、低功耗以及高靈活性等特點恰與新興技術“不謀而合”。

據Semico統計,FPGA市場正在逐年增長,而復合年均增長率高達38.4%,至2023年將具有55億-60億美元的規模。Achronix Semiconductor 總裁兼首席執行官Robert Blake表示對于FPGA近年的市場增長非常興奮,相信在龐大高速增長的市場中新產品將有出色的表現。

據統計,約有25%的企業選擇入局AI/ML以保持企業自身的競爭力,未來兩年內,將會有接近四分之三的企業會布局AI。而AI方面,算法仍在不斷演進,數值精度選擇越來越多樣性,但僅依賴數據格式的轉變降低能耗的方法已接近瓶頸,市場需要更具有高效計算力、高效大帶寬的數據運送能力、豐富儲緩存能力的最高能效比的廣適應性平臺。

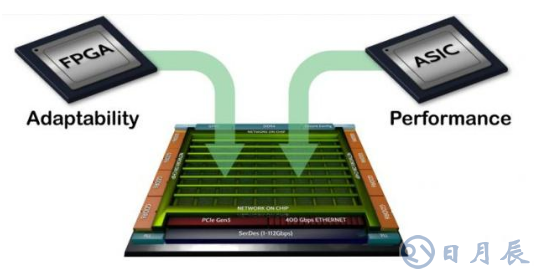

5月22日,Achronix宣布推出全新的 “FPGA+”系列產品Speedster7t FPGA,該產品采用臺積電(TSMC)7nm FinFET工藝打造。據介紹,該產品將FPGA與ASIC技術融合,兼顧了兩者的優點。

除此之外,Speedster7t FPGA具有革命性的新型二維片上網絡(2D NoC)和一系列針對高帶寬和人工智能/機器學習(AI / ML)應用進行了優化的新型機器學習處理器(MLP)。另外,值得一提的是,Speedster7t FPGA還具有滿足未來AI/ML需求所需的超高帶寬接口,包括400G以太網端口、用于數據傳輸的PCI Express Gen5端口以及用于業界最靈活、低成本、高帶寬存儲的GDDR6控制器。

利用四個架構代系的硬件和軟件開發基礎上的創新和積淀,客戶可以擁有更快的設計周期、更好的設計表現,另外,還可以降低設計中的風險、減少所需設計面積。

Blake表示:“我們正處于智能化、自學習計算的高增長階段的早期,這種計算將廣泛影響我們日的常生活。” Semico Research公司ASIC和SoC首席市場分析師Rich Wawrzyniak表示:“全新的系列產品是創新性芯片架構實現爆發的一個卓越案例,創造該架構的目的是直接面向AI應用處理大量的數據。”

如今,為了適應當前應用的高速發展,大多公司的設計團隊開始選擇全新的方案。眾所周知,ASIC具有高性能、低功耗的優勢,但相對來說,其內核執行外的任何算法都是凍結的,所以FPGA的高靈活性、高適應性相比來說更具優勢。那么,有沒有一款產品即具有FPGA的適應性,也兼顧ASIC的超高表現力?

Speedster7t FPGA系列產品正是將二者相融合,利用臺積電(TSMC)7nm技術,構建出全新的具有高性能、低功耗、高靈活性、高適應性的FPGA+。

假若將400G內容傳送到以太網比作在傳送帶上傳送,影響傳輸的除了傳送帶速度,還有盒子的大小。傳輸速度需要足夠快確保來得及裝包,而越大的盒子也會降低效率。傳統FPGA在傳輸400G內容時,無論如何調整傳輸大小和傳輸頻率,也無法達到以太網的傳輸曲線。所以對于傳統FPGA幾乎無法滿足超高速的傳輸條件。

來自Speedster7t高速I / O和存儲器端口的數萬兆比特數據很容易淹沒傳統FPGA面向比特位的可編程互連邏輯陣列的路由容量,而Speedster7t架構包含一個可橫跨和垂直跨越FPGA邏輯陣列的創新性的、高帶寬的二維片上網絡(NOC),它們連接到所有FPGA的高速數據和存儲器接口。

它們就像疊加在FPGA互連這個城市街道系統上的空中高速公路網絡一樣,Speedster7t的NoC支持片上處理引擎之間所需的高帶寬通信。NoC中的每一行或每一列都可作為兩個256位實現,單向的、行業標準的AXI通道,工作頻率為2Ghz,同時可為每個方向提供512 Gbps的數據流量。

通過在Speedster中實現專用二維 NoC,極大地簡化了高速數據移動,并確保數據流可以輕松地定向到整個FPGA結構中的任何自定義處理引擎。最重要的是,NOC消除了傳統FPGA使用可編程路由和邏輯查找表資源在整個FPGA中移動數據流中出現的擁塞和性能瓶頸。這種高性能網絡不僅可以提高Speedster7t FPGA的總帶寬容量,還可以在降低功耗的同時提高有效LUT容量。

傳統FPGA使用DSP模塊有著相對有限的表現力,具體表現在不高效的數值精度支持、需要消耗額外邏輯和Memory資源、性能受限于FPGA布線。

Speedster7t FPGA搭載全新的機器學習處理器(MLP),將計算、存儲和程序集于一身,使其支持陣列式乘累積計算架構、內嵌緩存、可配置以支持演進中算法、支持廣泛各種不同整點和浮點格式。大規模的可編程計算單元平行陣列是其核心,可提供業界最高的、基于FPGA的計算密度,另外,也具有最高的能效比。

MLP是高度可配置的、計算密集型的單元模塊,可支持4到24位的整點格式和高效的浮點模式,包括對TensorFlow的16位格式的支持,以及可使每個MLP的計算引擎加倍的增壓塊浮點格式的直接支持。

MLP與嵌入式存儲器模塊緊密相鄰,通過消除傳統設計中與FPGA布線相關的延遲,來確保以750 MHz的最高性能將數據傳送到MLP。這種高密度計算和高性能數據傳輸的結合使得處理器邏輯陣列能夠提供基于FPGA的最高可用計算能力以每秒萬億次運算數量為單位(TOPS,Tera-Operations Per Second)。

高性能計算和機器學習系統的關鍵之處是高片外存儲器帶寬,從而為多個數據流提供存儲源和緩沖。 Speedster7t器件是唯一支持GDDR6存儲器的FPGA,該類存儲器是具有最高帶寬的外部存儲器件。每個GDDR6存儲控制器都能夠支持512 Gbps的帶寬,Speedster7t器件中有多達8個GDDR6控制器,可以支持4 Tbps的GDDR6累加帶寬,并且以很小的成本就可提供與基于HBM的FPGA等效存儲帶寬。

“美光(Micron)樂于攜手Achronix去實現全球第一個面向高帶寬存儲需求而直接加載了GDDR6的FPGA產品,”美光計算與聯網業務部營銷副總裁Mal Humphrey。“像這樣的創新的和可擴展的解決方案將推動人工智能領域內的差異化,其中異構計算可選方案與高性能的存儲是加速獲得數據內涵的必需部分。”

非凡的存儲帶寬需要好的“后衛”才能真正發揮出其性能。Speedster7t器件包括業界最高性能的接口端口,以支持極高帶寬的數據流。

Speedster7t器件擁有多達72個業界最高性能的SerDes,可以達到1到112 Gbps的速度。還有帶有前向糾錯(FEC)的硬件400G以太網MAC,支持4x 100G和8x 50G的配置,以及每個控制器有8個或16個通道的硬件PCI Express Gen5控制器。

Speedster7t FPGA器件的大小范圍為從363K至2.6M 的6輸入查找表(LUT),無論是低成本客戶還是高端客戶,均可滿足。而FPGA+如此眾多的優點也可“隨意馳騁”在AI、圖像處理、語言處理、Database加速、加密算法、網絡處理方案上。

據Achronix表示,支持所有Achronix產品的ACE設計工具現已可提供,可支持包括Speedcore eFPGA和SpeedchipFPGA多晶粒封裝芯片(Chiplet)。相關配套軟件將于第三季度面世,更加高級的語言讓設計開發更具表現力,第一批用于評估的器件和開發板也將于2019年第四季度提供。