二極管是一種常用的電子元器件,它在ESD(靜電放電)防護(hù)中扮演了重要的角色。二極管的主要作用是允許電流只在一個(gè)方向流動(dòng),而阻止電流在另一個(gè)方向流動(dòng)。

在ESD防護(hù)中,二極管通常被用作"鉗位"設(shè)備,用于限制電壓的上升,防止電壓超過(guò)設(shè)備能夠承受的最大值。在ESD事件中,電壓可能會(huì)瞬間升高到很高的水平,如果沒(méi)有適當(dāng)?shù)谋Wo(hù),這可能會(huì)導(dǎo)致設(shè)備損壞。

二極管的工作原理是,當(dāng)電壓低于二極管的導(dǎo)通電壓時(shí),二極管處于關(guān)閉狀態(tài),不會(huì)有電流流過(guò)。然而,一旦電壓超過(guò)二極管的導(dǎo)通電壓,二極管就會(huì)導(dǎo)通,允許電流流過(guò)。這樣,二極管就可以將電壓"鉗位"在一個(gè)相對(duì)安全的水平,防止電壓過(guò)高。

在ESD防護(hù)中,通常使用特殊的二極管,稱為ESD保護(hù)二極管或TVS(瞬態(tài)電壓抑制)二極管。這些二極管被設(shè)計(jì)為在極短的時(shí)間內(nèi)響應(yīng),能夠處理高電流,并且具有低電容,這使得它們特別適合用于ESD防護(hù)。

總的來(lái)說(shuō),二極管在ESD防護(hù)中的主要作用是限制電壓的上升,防止電壓超過(guò)設(shè)備能夠承受的最大值。

二極管在早期IC電路的ESD防護(hù)中一直扮演著重要角色。即便現(xiàn)在二極管依然在ESD防護(hù)中發(fā)揮著重要的作用。這期就講一下二極管在ESD防護(hù)中的作用。在ESD防護(hù)中所應(yīng)用的二極管分為兩種:一種為二極管器件,一種為寄生二極管。這一期先講一下二極管器件。

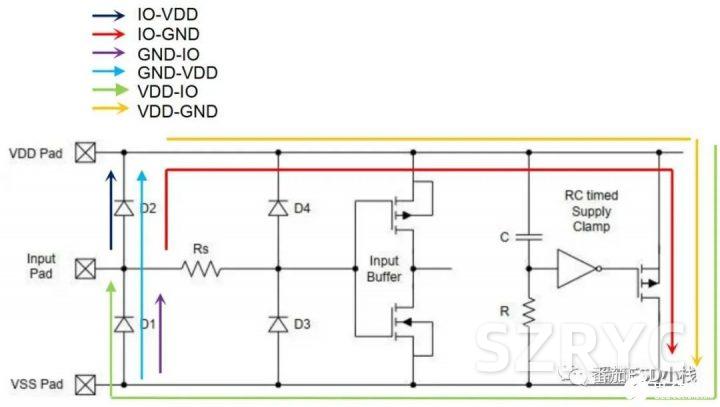

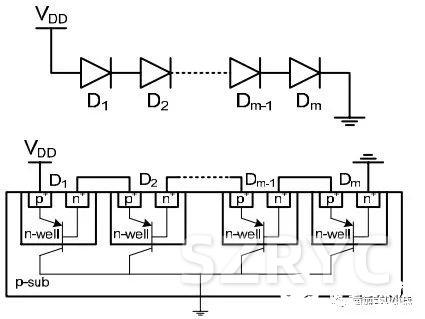

早期工藝都是使用單個(gè)反偏二極管作為ESD防護(hù)器件。但是這種設(shè)計(jì)方法只適用于大線寬工藝。隨著工藝的進(jìn)步,現(xiàn)階段的ESD防護(hù)策略已經(jīng)不建議二極管反偏擊穿泄放ESD電流,因?yàn)楝F(xiàn)在的工藝下需要更大面積才能避免二極管發(fā)生熱擊穿。(隨著線寬的減小熱擊穿與雪崩擊穿的界限也愈加模糊)?一.端口的ESD防護(hù)?現(xiàn)階段二極管通常與GCNMOS一起構(gòu)成ESD防護(hù)網(wǎng)絡(luò),二極管應(yīng)用于端口,GCNMOS作為Power Clamp,具體電路如下圖所示。

圖一.二極管+GCNMOS ESD網(wǎng)絡(luò)工作原理圖。 整個(gè)ESD網(wǎng)絡(luò)的工作原理如圖所示,整個(gè)網(wǎng)絡(luò)中,二極管都工作在正向?qū)ǖ那闆r下。通過(guò)二極管將IO端口的ESD泄放到VDD-Rail上,亦或是將GND-Rail上的ESD電路泄放到IO。當(dāng)ESD電流進(jìn)入VDD-Rail,RC觸發(fā)單元開(kāi)啟NMOS溝道,形成泄放通路。(Power Clamp 只能被VDD-Rail上的ESD觸發(fā)開(kāi)啟,具體細(xì)節(jié)可看前幾期淺談GCNMOS )如下圖所示,筆者還見(jiàn)過(guò)另外一種ESD網(wǎng)絡(luò)。

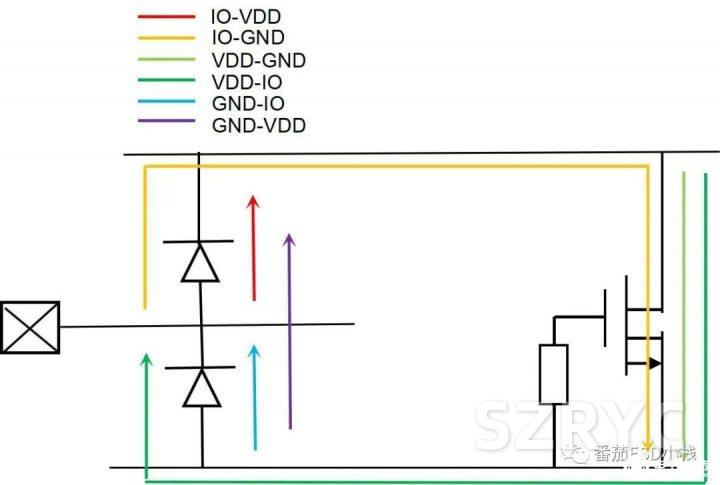

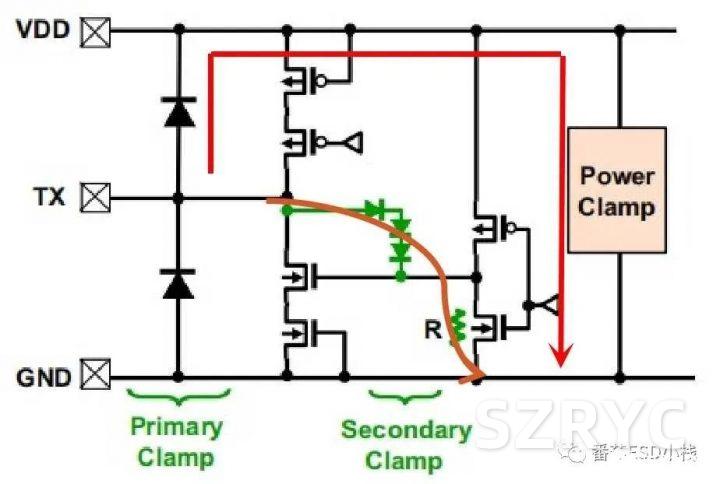

圖二.二極管+GGNMOS ESD網(wǎng)絡(luò)工作原理圖。 圖一的ESD網(wǎng)絡(luò)屬于頻率觸發(fā)機(jī)制,而該ESD網(wǎng)絡(luò)屬于電壓觸發(fā)機(jī)制。端口到GND的泄放路徑的Trigger Voltage為正偏二極管+ GGNMOS,這種設(shè)計(jì)會(huì)提升ESD網(wǎng)絡(luò)的Trigger Voltage。一般用于多電壓域共地電路,如果多電壓域采用GCNMOS作為Power Clamp,那么每個(gè)電壓域都需要一個(gè)RC觸發(fā)電路,面積不劃算。?二.Gate Clamp?還可以用二極管實(shí)現(xiàn)Gate Clamp 技術(shù)。該技術(shù)簡(jiǎn)而言之就是使用二極管將MOS管的源/漏與柵端進(jìn)行連接,利用二極管的鉗位特性保護(hù)易出現(xiàn)失效的MOS管。

圖三.Gate Clamp應(yīng)用實(shí)例。 通過(guò)控制二極管串的數(shù)量,調(diào)整Gate Clamp的Design Window使其在正常工作時(shí)關(guān)閉,發(fā)生ESD時(shí)開(kāi)啟。要求其開(kāi)啟電壓要大于Absolute?Max的1.1倍,小于柵漏的BreakDown Voltage 。從而實(shí)現(xiàn)對(duì)Main driver中NMOS的保護(hù)。

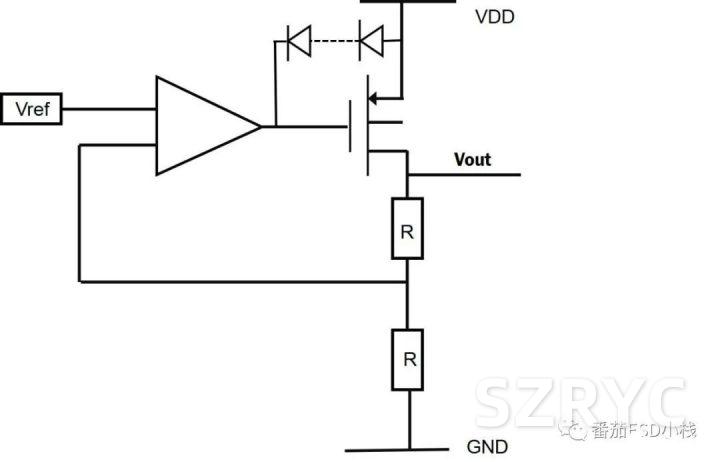

圖四.LDO中Gate Clamp的應(yīng)用。 另外筆者也對(duì)電源管理芯片中LDO的功率管設(shè)計(jì)過(guò)Gate Clamp技術(shù),因?yàn)槭褂脠?chǎng)景中VDD上會(huì)存在浪涌,為了保護(hù)LDO的功率管,在PMOS的源端與柵端連接了二極管串。通過(guò)控制二極管的數(shù)量,確保正常工作時(shí)VDD與誤差放大器的壓差無(wú)法開(kāi)啟Gate Clamp。當(dāng)VDD發(fā)生浪涌時(shí),通過(guò)Gate Clamp鉗住功率管的VGS,起到保護(hù)的作用。(這個(gè)方案后續(xù)作廢了,這里只是為從ESD保護(hù)的角度為讀者提供思路,便于理解。)?三.二極管串?二極管串也可以作為Power Clamp,如圖所示。

圖五.二極管串及刨面圖。

使用二極管串作為Power Clamp的工作原理與Gate Clamp類似,通過(guò)調(diào)整二極管的數(shù)量,控制二極管串的開(kāi)啟電壓位于Design Window內(nèi)。但是這種設(shè)計(jì)目前有兩個(gè)弊端:

1.二極管是典型的Non-Snap-Back器件,其開(kāi)啟后IV特性還會(huì)表現(xiàn)出一定斜率,所以其防護(hù)性能不如GGNMOS等Snap-Back型器件。

2.二極管串與襯底間存在寄生三極管,會(huì)構(gòu)成達(dá)林頓組態(tài),從而導(dǎo)致開(kāi)啟電壓的進(jìn)一步降低。為了保持足夠高的開(kāi)啟電壓,需要串聯(lián)更多的二極管,但是更多的二極管又會(huì)增強(qiáng)達(dá)林頓組態(tài)。所以二極管串作為Power Clamp的設(shè)計(jì)并不多見(jiàn)。

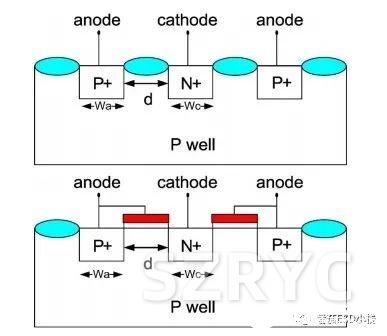

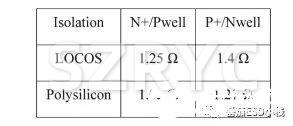

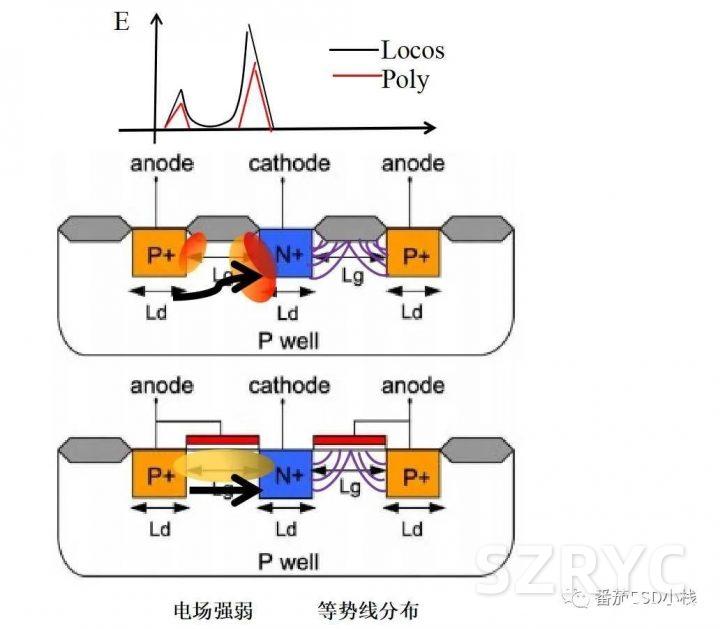

四.Locos-Bound 二極管與Polysilicon-Bound二極管?常見(jiàn)的二極管都是STI或者LOCOS作為隔離結(jié)構(gòu),但是現(xiàn)階段為了提高ESD能力,出現(xiàn)了以Poly作為隔離結(jié)構(gòu)的Polysilicon-Bound,具體如圖所示。

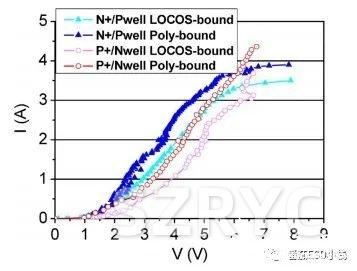

圖六.Locos-Bound?diode與Polysilicon-Bound diode。 Locos-Bound diode陰極與陽(yáng)極有源區(qū)間采用LOCOS作為隔離結(jié)構(gòu),而Polysilicon-Bound diode陰極與陽(yáng)極間采用多晶硅作為隔離結(jié)構(gòu)。后者具有更加優(yōu)秀的電流承載能力與更小的開(kāi)啟電阻,Polysilicon-Bound diode的二次擊穿電流It2與開(kāi)啟電阻Ron都優(yōu)于傳統(tǒng)Locos-Bound diode。

圖六.Locos-Bound diode與Polysilicon-Bound diode IV曲線對(duì)比。

圖七.Locos-Bound diode與Polysilicon-Bound diode 開(kāi)啟電阻對(duì)比。

圖八.Locos-Bound diode與Polysilicon-Bound diode電場(chǎng)分布圖。 無(wú)論Locoss-Bound diode還是STI-Bound diode都會(huì)因?yàn)檠趸锔綦x而在有源區(qū)邊緣引入應(yīng)力,從而造成晶格適配形成勢(shì)壘,使得電場(chǎng)在有源區(qū)與隔離的接觸面更為集中。另一方面氧化物隔離的存在會(huì)使得電場(chǎng)線分布更加密集。反之,Polysilicon-Bound diode 整個(gè)N-Well較為均勻,晶格缺陷與位錯(cuò)較少。電場(chǎng)分布均勻,且電場(chǎng)線在有源區(qū)邊緣也較為均勻。這使得Polysilicon-Bound diode具有均勻的電場(chǎng)分布和更加優(yōu)秀的載流子遷移率。更為直觀解釋便是Polysilicon-Bound diode的載流子遷移路徑更短(不需要繞過(guò)氧化物隔離),阱電阻更低,所以過(guò)電流能力強(qiáng),開(kāi)啟電阻低。但是相對(duì)的,Polysilicon-Bound diode的擊穿電壓會(huì)略低于Locos-Bound diode(從數(shù)據(jù)上看差距并不明顯)。

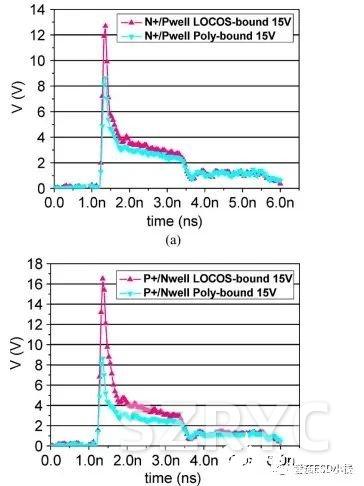

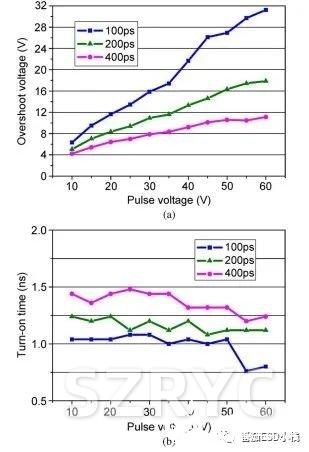

同時(shí)得益于器件內(nèi)異質(zhì)結(jié)電容的減少(異質(zhì)結(jié)容值較小,只對(duì)ps級(jí)別的CDM放電產(chǎn)生影響),Polysilicon-Bound diode表現(xiàn)出更優(yōu)異的CDM防護(hù)性能。如圖所示,Polysilicon-Bound diode在VFTLP下的過(guò)沖電壓遠(yuǎn)低于Locos-Bound diode,同時(shí)其對(duì)高頻CDM具有良好的開(kāi)啟時(shí)間。

圖九.Locos-Bound diode與Polysilicon-Bound diode在VFTLP下的過(guò)沖電壓。

圖十.Polysilicon-Bound diode在VFTLP不同上升脈沖下的過(guò)沖電壓與開(kāi)啟時(shí)間。?針對(duì)CDM放電,開(kāi)啟時(shí)間的重要性遠(yuǎn)大于泄電流能力。所以Polysilicon-Bound diode針對(duì)CDM放電具有更加優(yōu)異的表現(xiàn)。目前筆者所接觸的國(guó)產(chǎn)工藝中還沒(méi)有見(jiàn)過(guò)Fab提供Polysilicon-Bound diode的標(biāo)準(zhǔn)單元,可能SMIC的先進(jìn)工藝會(huì)提供該二極管的pdk。相較于SCR筆者認(rèn)為這種二極管推廣難度更低,也確實(shí)能在一定程度上提高ESD性能。