什么是芯片反向設計?它是通過對芯片內部電路的提取與分析、整理,實現對芯片技術原理、設計思路、工藝制造、結構機制等方面的深入洞悉,可用來驗證設計框架或者分析信息流在技術上的問題,也可以助力新的芯片設計或者產品設計方案。

芯片反向工程的意義:現代IC產業的市場競爭十分激烈,所有產品都是日新月異,使得各IC設計公司必須不斷研發新產品,維持自身企業的競爭力。IC設計公司常常要根據市場需求進入一個全然陌生的應用和技術領域,這是一件高風險的投資行為。并且及時了解同類競爭對手芯片的成本和技術優勢成為必然的工作。如果讓工程師在最短的時間以最有效率的方式設計電路才是最難解決的問題,逆向工程看來是其中一個解決方案。逆向工程能將整顆IC從封裝,制成到線路布局,使用將內部結構,尺寸,材料,制成與步驟一一還原,并能通過電路提取將電路布局還原成電路設計。

目前,國外集成電路設計已經非常成熟,國外最新工藝已經達到10nm,而國內才正處于發展期,最新工藝達到了28nm。有關于集成電路的發展就不說了,網絡上有的是資料。對于IC設計師而言,理清楚IC設計的整個流程對于IC設計是非常有幫助的。然而,網絡上似乎并沒有有關于IC設計整個流程的稍微詳細一點的介紹,僅僅只是概略性的說分為設計、制造、測試、封裝等四大主要板塊,有的資料介紹又顯得比較分散,只是單獨講某個細節,有的只是講某個工具軟件的使用卻又并不知道該軟件用于哪個流程之中,而且每個流程可能使用到的工具軟件也不是太清楚(此觀點僅為個人經歷所得出的結論,并不一定真是這樣)。

芯片正向設計與反向設計。目前國際上的幾個大的設計公司都是以正向設計為主,反向設計只是用于檢查別家公司是否抄襲。當然,芯片反向工程原本的目的也是為了防止芯片被抄襲的,但后來演變為小公司為了更快更省成本的設計出芯片而采取的一種方案。目前國內逐漸往正向設計轉變的公司也越來越多,正逐漸擺脫對反向設計的依賴。當然,正處于發展初期的公司也不少,自然反向設計也是不少的。本文章從芯片反向設計開始進行總結。“工欲善其事,必先利其器”。隨著集成電路的不斷發展,不管是芯片正向設計還是反向設計,它們對于工具的依賴性越來越強,因此,在要開始講設計流程之前,先來看一看,我們到底會用到哪些主要的工具和輔助性的軟件。

主要工具軟件說到設計工具,就不能不提到三大EDA廠商——cadence,synopsys,mentor。這三家公司的軟件涵蓋了芯片設計流程的幾乎所有所能用到的工具。首先是cadence公司,這家公司最重要的IC設計工具主要有candence IC系列,包含了IC 5141(目前最新版本是IC617),NC_VERILOG(verilog仿真),SPECTRE(模擬仿真),ENCOUNTER(自動布局布線)等等synopsys公司,最出名的是它的綜合工具design complier,時序分析工具prime time,模擬仿真工具hspice等;mentor公司最出名的工具是calibre(版圖DRC LVS檢查),modelsim(verilog仿真)。這些都是IC設計最常用的工具,無論是正向設計還是反向設計。當然,隨著軟件版本的更新迭代,軟件的名字可能有所變更,并不是上述的那些名稱。另外,這些工具主要集中在以linux為內核的操作系統上,主要代表有Red Hat。所以有關unix\linux類操作系統的知識還是有必要學的,該類系統與windows系統有很大的不同,要想學會使用這些軟件,首先要學習這些操作系統的相關知識,具體資料網上有很多。部分工具有windows版本,例如hspice,Modelsim。

輔助類工具軟件當然,除了這三大EDA廠商的IC設計工具外,Altera 、Xilinx、KeilSoftware這三家公司的軟件quartus ii、ISE、KEIL開發環境等,都是對于IC設計流程中比不可少的工具。它們分別是用于FPGA、單片機ARM芯片的開發。這類軟件在芯片的CP測試和芯片應用方案開發上會有用到。版圖提取工具,NetEditorLite、ChipAnalyzer,這兩個工具主要是針對芯片反向設計而言的。算法設計工具,MATLAB,此工具應用范圍很廣,但對于芯片設計來說,它較為適用于算法原型開發,例如,通信算法。PCB版圖工具,Altium Designer,Orcad,Allegro。其中,目前Orcad,Allegro是屬于cadence電路系統設計套件內的主要軟件,而Altium Designer是最常用的軟件,它的前身是Protel。Labview與數字源表,這一對軟硬件主要用于芯片電氣參數的半自動化測試,特別是模擬芯片。其目的是芯片設計公司用于分析芯片樣品參數用。對于這些工具的該如何使用,我會在下面的文章中進行說明。ps:沒有具體說明軟件使用環境的,一般是在windows環境下使用。先從反向設計說起。下面是我整理的芯片反向設計的流程圖。

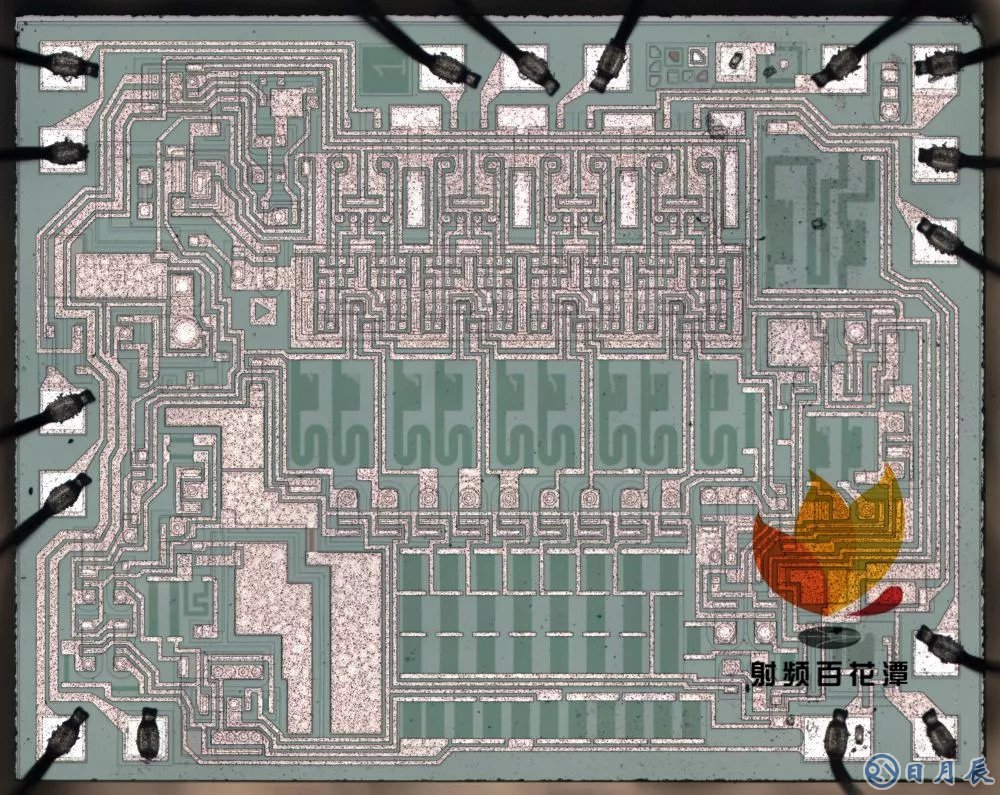

一、反向設計總體規劃在進行一塊新品芯片的開發前期必須要有一個設計總體規劃,其中最主要的問題就是,這顆芯片是否能帶來收益,畢竟公司要靠產品吃飯。如何評估芯片能否帶來收益?這需要多年的經驗才能進行準確的評估。一般是看市場上哪幾款芯片銷量好,并且未來幾年的銷量看漲,并且評估本公司是否有能力設計并且有渠道銷售出去。要考慮的芯片成本有以下幾項:1,芯片拍片成本;2,芯片從立項到交貨的時間成本,時間過程導致芯片即使設計出來了,市場已經不需要了;3,流片成本;4,工具軟件的授權使用成本;5,測試成本,包括CP測試和成品測試以及搭建測試平臺所需要的其它成本;6,封裝成本。將這些成本進行適當預估之后,再來看收益。對于收益這塊,這是和市場的需求和銷量走向有關,需要涉及到許多其他方面的考慮。在收益問題解決了之后,明確此項目可以獲得收益,那么就可以正式開工,前面說的一堆東西其實就是項目可行性分析的一部分。但其實有些公司并不會考慮那么多,因為這些可行性分析本身非常困難。反向哪一家的芯片?選擇大公司的芯片進行反向一般來說成功率會更高。選定芯片后就進行拍片了,芯片進行解剖拍片一般周期在1周到1個月之間,這視芯片的大小而定。

二、工藝選擇這個要依據拍片回來的芯片版圖來決定,通過對芯片版圖的識別,判斷待反向的芯片版圖使用的工藝是什么,再根據公司自己擁有的工藝文件(這些工藝文件都由國內或者國外的芯片制造廠提供,前提是公司得與它們合作才能得到工藝文件),兩者進行比對,選擇一個適合的工藝進行后續的仿真、版圖繪制和流片。工藝選擇的問題,需要對公司所擁有的工藝非常熟悉,并且對版圖也要熟悉的工程師來解決,他要能夠通過版圖明確的識別所用的工藝。當然,工藝有時候會在設計過程中反復的更換,因為會有許多參數、流片成功率等各種復雜因素的考量。這一步其實也就叫工藝可行性分析,其實也應該歸于項目可行性分析的一部分,但是由于必須要拍片才能進行,所以只能單獨說明。

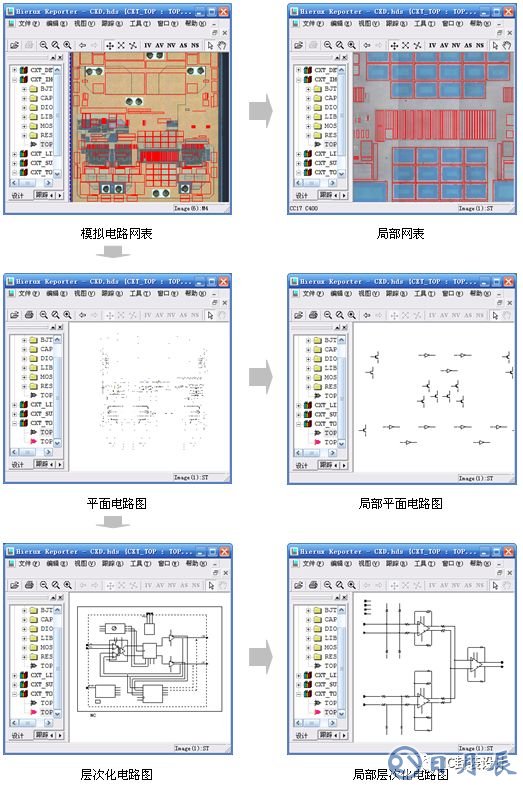

三、版圖提取在上一步工藝可行性分析完之后,確認有工藝可以和該版圖匹配,那么就可以進行版圖提取工作。這部分的工作其實主要是識別版圖中的管子并用符號表示出來。所用到工具有NetEditorLite或者ChipAnalyzer,這是版圖提取工具,在不同的公司進行芯片拍片,會用到不同的版圖提取工具。該類軟件的作用就是一個圖片查看器,拍攝的版圖就是數據就是照片。cadence IC5141 里的virtuoso schematic軟件,這是電路圖繪制軟件。整個工作的流程是用NetEditorLite或者ChipAnalyzer打開拍片的芯片版圖數據,人工肉眼識別里面的管子(二極管、三極管、MOS管之類),再使用virtuoso schematic將管子用符號表示出來,并把管子之間的連接關系連接上。版圖提取所要注意的問題:初次進行版圖提圖,可能會不認識管子,需要有經驗的人來幫助識別,熟悉之后就容易了;不同工藝的版圖管子的形狀是不一樣的,所以碰到不認識的管子,要么靠別人幫忙,要么就只能自己去推理;要有良好的管子命名習慣,這個每個公司都應該有規定的,這對于后續的工作會有很大幫助;盡量按照版圖的布局來放置管子的布局(在virtuoso schematic上的電路圖布局),這樣可以加快以后對比電路圖和版圖時找管子的速度;在整理提取出的電路時一定要新建一個電路圖來放置整理的電路,不要在剛提取的電路圖上整理,方便整理時和版圖數據對比。

四、電路整理在版圖提取完畢之后,下一個步驟就是電路整理。提取完的電路圖是混亂的,沒有層次關系。那么如何將其整理成具有層次關系,讓人一看就懂呢?1、這就涉及到有關芯片的一些常識了。芯片分為數字芯片和模擬芯片,但是數字芯片必定會包含模擬電路,而模擬芯片卻可以不包含數字電路。它們有如下一般特征:A、數字芯片,必有時鐘振蕩電路、復位電路這些模擬電路。必有寄存器,而且整個數字部分最耗面積的部分往往都是寄存器。寄存器的使用量是很大的,因此,在版圖上呈現的就是有大數量的圖像一模一樣的電路,這種電路往往都是寄存器。B、模擬芯片,有帶隙基準電路。2、說完了芯片版圖常識,另外一個重要的有助于理解所提取的電路的工具就是待反向的芯片的數據手冊!這是最重要的,我們所有有關于芯片的信息都是從數據手冊上得來的。所以一定要善用DATASHEET!在芯片數據手冊上,一般會對芯片的功能進行說明,對芯片如何運行進行說明,這些說明將有助于我們對于電路的整理。比如說,芯片手冊上說道用了I2C,那么電路中肯定有一大塊電路是屬于I2C的。一般來說,版圖的布局都是將同屬于一種功能的管子會集中放置在一起。I2C電路的特征,從I2C協議的原理上可以知道,它就兩根信號線,一根時鐘,另一根數據線。數據在芯片內部一般是并行傳輸比較方便,所以,I2C電路一定會有串并轉換電路,而串并轉換電路一般是寄存器,而且一般是8位。根據這個推斷結果,就在提取的電路中去尋找8個在一起的寄存器,它們其中一組就是I2C電路的一部分,再根據芯片版圖的I2C PAD位去尋找,看連接到了那一組寄存器上,那么整個I2C的電路就被識別出來了。因此,a、靠著芯片手冊對芯片功能的說明,b、加上芯片的一些常識性知識,c、加個人的這種對電路原理的推理,就可以相對較快的將電路分層次的整理出來。逐步的理解整個芯片的原理。當然,由于芯片電路的龐大的關系,有時候電路并不是需要完全理清楚,對于不那么重要的電路可以不理會。只要保證連接關系沒連接錯就行。這階段,只會用到cadence ic5141的virtuoso schematic軟件。

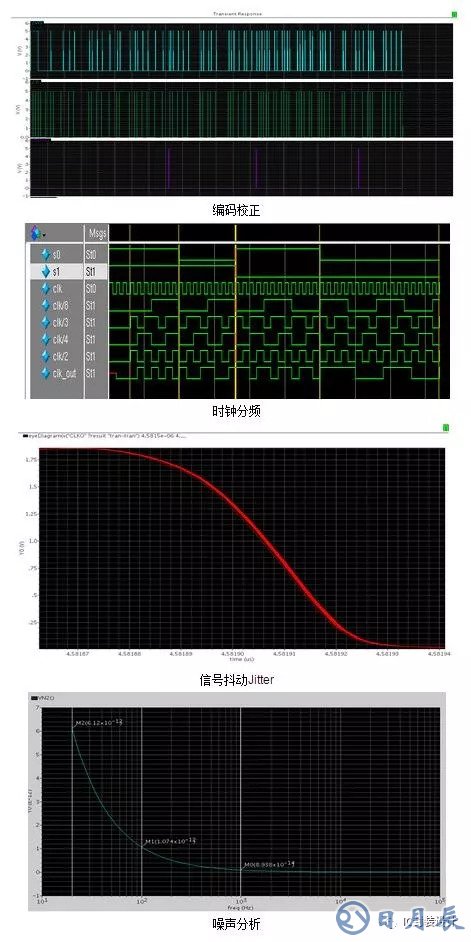

五、 電路仿真及修改電路整理好了,下一步就是進行電路的仿真及修改了,根據工藝選擇步驟選擇的工藝來進行。先說明一下這階段所使用的工具:1、cadence spectre,一般集成在cadence ic5141里面,是模擬電路仿真工具(ps:最原始的版本是集成在IC5141內部,但功能不全,所以需要單獨安裝新版本,軟件名為MMSIM61,隨著版本的升級,它的名字也在修改),當然,數字電路也可以進行仿真,數字電路的本質還是模擬電路;2、synopsys公司的 Hspice,與spectre一樣的仿真工具,另有些差別。3、Mentor公司的 Modelsim,主要在windows上使用,用于verilog網表的仿真。模擬電路仿真工作流程:在cadence中搭建好仿真環境,設置好仿真參數,選用spectre或者hspice,然后就可以進行仿真的。另外,也可以將電路導出成CDL網表,拷貝到Windows上,用Windows版本的Hspice進行仿真,這樣做的優點是Windows易于操作。另外說明一下spectre和hspice的一項區別。spectre仿真的時候會保存所有電路節點的數據,這樣做優點是方便查看各個節點的數據,缺點是仿真消耗的時間太長,保存的數據文件太大,這一點在遇到大型電路的時候會很耗時(不知道最新版本改進這一點沒有,鄙人沒有用過最新版的spectre)。hspice仿真之前可以自己選定所要查看的節點,這樣做就可以減少仿真時間和減小數據文件的大小。數字電路仿真工作流程:在virtuoso schematic中將整理好的電路路中數字電路部分導出成網表文件,再拷貝到windows系統上進行仿真。windows系統上數字電路網表的仿真采用Modelsim。(這么做的原因是linux系統不太方便)使用Modelsim仿真,最重要的是寫好testbench(貌似這句是廢話)。關于電路的修改,這部分其實不好總結,因為每一款芯片都有不同的參數,所要修改的地方都不太一樣,我所知道的是,必定要考慮修改的地方往往都是有關模擬電路的,例如,時鐘振蕩、復位電路、開漏輸出管、帶隙等,修改的目的是為了與當前所選用的工藝適配,以滿足芯片datasheet的參數要求。另外,數字部分的電路其實一般來說是不需要修改的,但有時為了節省版圖面積,會縮小寄存器管子的尺寸,畢竟縮小一個,就等于縮小了幾十個。這一階段其實是一個不斷的迭代過程,它要和版圖繪制結合起來,這樣才能夠保證芯片功能和性能的完整。

六、版圖繪制這部分在電路整理完之后就可以開始進行了,并配合電路仿真與修改,逐步晚上版圖的繪制。該階段所使用的主要工具有 1、cadence ic5141的版圖繪制軟件;2、cadence Dracula Diva或者Calibre,這兩個用于版圖DRC(設計規則檢查)、LVS(版圖一致性檢查);一般而言,calibre會更加常用一些,畢竟這可是Mentor公司的招牌軟件之一。在版圖繪制好并進行各種檢查無誤之后,就可以tapeout,準備流片了。

七、測試規范IC設計師在芯片tapeout之后就要準備制定CP測試規范了,這是接下來CP測試流程的總綱,非常重要。測試規范的測試項主要來源于芯片datasheet,將重要的參數設置為測試項,并規定參數的合理分布范圍以及每一個測試項的測試方法(流程)。這些測試參數以及測試方法將決定CP測試開發時所用到的測試環境ATE(auto test environment)。

八、CP測試開發根據測試規范,可以選定所需要的測試工具以進行整個測試環境的搭建工作。我所知道到用于芯片測試的測試儀有JUNO DTS-1000,ASL1000,V777,STS8200等。每一種測試儀適用于不同種類的芯片測試,測試儀主要分為數字測試,模擬測試,數模混合測試這三大類。CP測試開發所需要做的工作有:1,測試儀的選擇(ps:這個階段還要考慮一個重要的因素就是一次測試多少顆裸芯,也就是CP測試常說的多少個site,這關系到后續測試程序的編寫,以及DUT板的制作,非常重要);2,根據測試儀開發測試程序;3,制作測試裸芯片用DUT板,扎PAD位的針由測試廠制作并焊接在DUT上(ps:DUT板有時候也叫針卡);4,自制測試儀(可選),當測試儀并不能完成某些特殊測試項的要求時,還得自己制作測試儀。例如,紅外接收芯片測試所需要用到的掃頻儀,若采用非自制掃頻儀,測試時間將非常長,必須自己制作。5,測試數據的分析。對測試數據的分析有助于對測試方法的改進和對芯片設計的改進。CP測試在整個芯片反向設計中占據著重要位置,所花費的人力、物力是非常多的,還需要頻繁和測試廠交流,所以CP測試顯得非常復雜。在CP測試開發完之后,會進行COB測試,之后才進行CP測試的調試階段,以及正式批量測試階段。

九、COB測試所謂COB測試,其實就是Chip On Board(將裸芯打線在PCB板上或者將封裝好的芯片焊接在PCB上,并將引腳引出),它是在CP測試進行之前進行的一項測試(也在成品測試之后進行),用于初步判斷芯片的功能和性能,如果這批次隨機采樣的幾顆芯片功能和性能都很爛就暫時不必進行CP測試了。另外,COB測試相比于CP測試具有更多的靈活性,可以測試更多的測試項,獲取有關芯片更為全面的信息。當然,COB測試也是需要開發一套相應的測試環境的。開發的工作根據芯片的不同,工作量會有很大的不同,例如,如果有I2C通信引腳的芯片,需要用到USB轉I2C芯片,例如FT232。通過在電腦上編程,通過控制USB轉I2C芯片來控制待測芯片。這樣的話,搭建整個測試環境就會比較復雜。如果是模擬芯片,例如電源管理類芯片,需要使用LabView編程來控制數字源表進行自動化參數測量。總之,COB測試也是芯片設計中一個比較重要的流程,這部分的工作內容,比較難以敘述,簡單的,就用數字源表測試幾項參數就行了,復雜的都會基于軟件控制的形式進行半自動的測試。具體說來,1、開發在PC端開發測試的程序,例如LabView;2、設計測試芯片的電路板,并留下與PC通信的接口,通常采用單片機做主控芯片;3、搭建測試所需要的環境,比如說遮光要求。過程敘述得很簡單,但實際開發并不容易,難度視待測芯片而異。

十、成測開發在CP測試完了之后,裸芯就可以送到成測廠進行劃片和封裝了,在這期間,IC設計師所要做的工作就是依據制定成品測試的規范并進行成品測試的開發。這部分的工作其實和CP測試的工作是類似的,只不過,相對于CP測試而言,成品測試的測試項會少很多。許多CP測試用到的測試項,比如,燒調之類的,成品測試就不會進行了,其余步驟均與CP測試一致。

十一、可靠性測試當芯片封裝好,并通過了成品測試之后,并不意味著芯片的測試就結束了,還有芯片可靠性測試。在成測結束,并把樣品返回設計師手中之后,設計師還需進行COB測試,并在這時預留幾顆芯片不參與接下來的可靠性測試,這幾顆芯片將在可靠性測試之后作為對比之用。芯片可靠性測試,是衡量芯片的質量和壽命的一項測試。它具體包括環境測試、EMC測試、其它測試等三大項。細分項有高溫低溫測試、高溫高濕測試,抗靜電測試等等,全部的測試項可參考IC可靠性測試項目。每一款芯片都有與其對應的可靠性測試項,并不是所有測試項目都要測。我們只要關注與該芯片適配的測試項就行。具體如何決定測試項,這需要與芯片的用途有關,每一種用途,它的測試要求都是不一樣的。可靠性測試實驗比較簡單,但是,芯片的可靠性卻是由此來衡量的。可靠性測試需要的測試工具都比較昂貴,當然工具的重復使用性也是比較好的。每一個測試項都對應這一套測試設備。

十二、成品開發設計出的芯片必須配置相應的使用方案,才能將芯片推廣出去,客戶才能夠更好的使用芯片。不同用途的芯片,它的使用方案不一樣,差別也是非常巨大的。像單片機、ARM、FPGA類芯片,配置的可不是簡單的使用方案,而是一整套使用它的系統。電源管理芯片,需要配置一個電源管理芯片的一套應用方案,并且需要具有一定的競爭力,這才能夠將芯片賣出去。所以成品開發是芯片能否賣出去的關鍵。我所接觸到的成品開發,基本是以單片機為主控芯片的開發方案。具體開發過程將在后續有更為詳細的說明。